- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

利用Cadence PCB SI分析特性阻抗变化因素

1、概要

在进行PCB SI的设计时,理解特性阻抗是非常重要的。这次,我们对特性阻抗进行基础说明之外,还说明Allegro的阻抗计算原理以及各参数和阻抗的关系。

2、什么是特性阻抗?

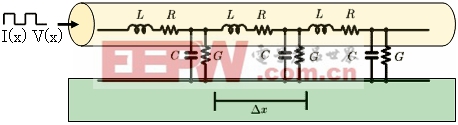

2.1 传送线路的电路特性

在高频率(MHz)信号中,把传送回路作为电路。

2.1.1 电阻R

电阻R是指普通的导线带有的欧姆电阻。R = ρL / S [Ω] (S:横截面面积[m2],L:导体长[m],ρ:金属(铜)的电阻率[Ω*m])。在高频频域范围内的话,根据表面效果和集合效果的影响,集中在导体表面电流流动,会使上面公式中的阻值变得更大。

2.1.2 电容C

电容C是指积蓄在导体间电荷的量。C = ε(S / d)[F] (ε:介电常数,S:导体的横截面积,d:导体间的距离)

2.1.3 电感L

电流流动的导线必定有磁通量发生,根据这个产生的自感。L=0.002S[2.3lg(2s/w+t)+0.5][μH] S:导线长度(cm) ,W:导线宽度(cm), t:导线厚度(cm)

2.1.4 电导G

物体传导电流的本领叫做电导。对导体间的介电特性的反抗成分,表示容易电流的程度。G = 1 / R

2.2 阻抗和特性阻抗的不同?

阻抗

表示电路部分对交变电信号流通产生的阻力,是传输线上输入电压对输入电流的比率值Z = V(x)/ I(x)

特性阻抗

特征阻抗是指信号沿传输线传播时,信号看到的瞬间阻抗的值。简单地讲,无限长传输线上各处的电压与电流的比值定义为传输线的特性阻抗。Z0 = √( (R + jωL) / (G + jωC) ) P √(L / C)(RωL,GωC)

3、Allegro的特性阻抗计算原理

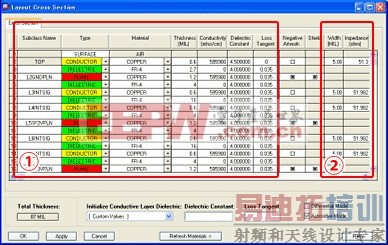

3.1 在Layout Cross Section中阻抗计算

PCB SI菜单的Setup >Cross-section

单线的特性阻抗计算方法>

1.设定层结构和材料物质。

2.Width栏输入线宽的话,在Impedance栏会计算出特性阻抗。(Impedance输入目标阻抗的话,则会计算线宽。)

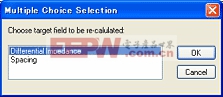

差分阻抗>

1.勾选Differential Mode

2.设定层结构和材料物质。

3.Coupling Type设定结合类型。(NONE: 不耦合,EDGE:同层耦合,BROADSIDE:邻接层耦合)

4.因为设定线宽的话,确定差分阻抗或者spacing任何一个,选择Spacing单击OK按钮,差分阻抗被计算。[p]

(如果想指定差分阻抗的,设定DiffZ0,调节线宽和spacing。)

D 参考1 D

层结构计算过阻抗之后,可以通过PCB Editor菜单的File >Export >Techfile技术文件进行保存,再利用。根据这个,可以通过程序库管理本公司阻抗设计的经验技术。

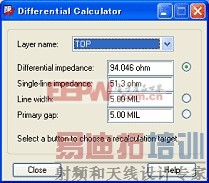

3.2 在Electrical Constraints中计算阻抗

PCB Editor菜单的Setup >Constraint单击Electrical constraint sets按钮,选择DiffPair Valuetab,并且单击Calculator按钮。

能用上述方法计算差动阻抗时,层结构Layout Cross Section是已经设定,不能修改的。

3.3 在View Trace Model Parameters中计算阻抗

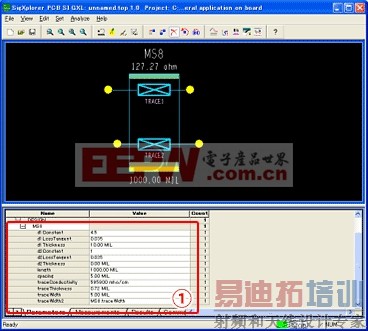

SigXplorer菜单的Edit >Add Part,Model Type Filter选择Interconnect,选择想使用的传送线路模型,界面配置。

1.以SigXplorer画面的参数界面,设定层构成和材料属性,线宽和线距。

2.以SigXplorer画面的参数界面,在对象模型的地方进行单击右键,选择View Trace Parameters。

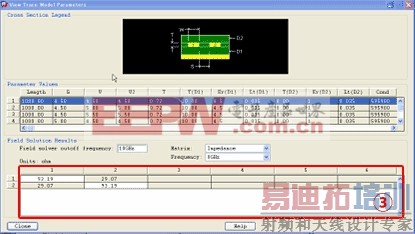

3.在View Trace Model Parameters界面内,Field Solution Results内Field solver cutoff frequency设定10GHz,Matrix设定Impedance,特性阻抗以矩阵形式被表示。(如果想使之表示差分阻抗的情况, Matrix设定Diff Impedance。)

D 参考2 D

如果在范围内设定了分步或复数的价值,View Trace Model Parameters的Parameter Values会以列表的方式列出所有的数据。

D 参考3 D

Field Solution Results栏,能表示以下的结果。

Capacitance

Die. Conductance

Inductance

Linear Resistance

Modal Velocity

Admittance

Impedance

Diff Impedance

Near-End Coupling

Modal Delay

在Capacitance/ Die. Conductance/ Inductance/ Linear Resistance中,能够设定频率。

4、各参数和特性阻抗Z0的关系

本项,使用「在3.3 View Trace Model Parameters的阻抗计算」介绍的功能,确认各参数和特性阻抗Z0的关系。

4.1 计算单线的特性阻抗Z0

Z0和各参数的关系如下图,研究只变化一个参数的时候,特性阻抗Z0的变化。

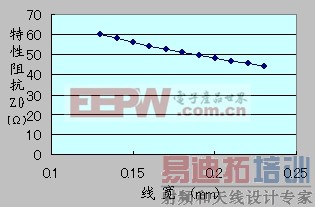

4.1.1 用图表表示在线宽W和让特性阻抗Z0的关系

线宽W在0.13~0.23mm范围内,以0.01mm间隔变化了11点的时候,特性阻抗Z0的变化。

从这个图表可以看出,线宽W变大,特性阻抗变小。线宽W变大的话,导体与参考面之间的电容C和导体的电感L也变大,不过,对特性阻抗Z0的影响是因为电容C变大。默认的电容C和电感L的价值。「电容C =110.2pF, 电感L=286nH」[p]

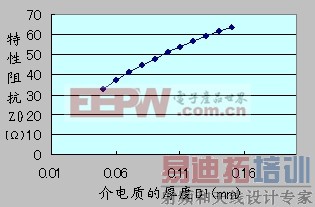

4.1.2 用图表表示介电质的厚度D1和特性阻抗Z0的关系

介电质厚度D1在0.05~0.15mm范围内,以0.01mm间隔使之变化了11点的时候,特性阻抗Z0的变化。

从这个图表可以看出,介电质厚度D1变大,特性阻抗Z0变大。因为参考面与导体的距离变大,导体和参考面间的电容C变小。

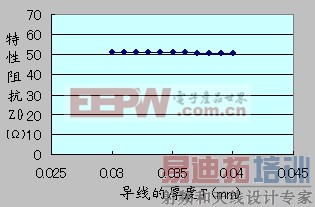

4.1.3 用图表表示让导线的厚度T和跟特性阻抗Z0的关系

导线的厚度T在0.03~0.04mm范围内,以0.001mm间隔变化了11点的时候,特性阻抗Z0的变化。

从这个图表可以看出,导线的厚度T变大,特性阻抗Z0一点点变小。导线的厚度T变大的话,与导体间的电容C和导体的电感L也变大,不过,对特性阻抗Z0的影响因为是电容C变大。

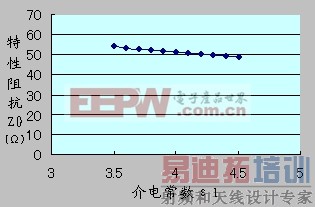

4.1.4 用图表表示跟介电常数ε1和特性阻抗Z0的关系

介电常数ε1在3.5~4.5范围内,以0.1间隔变化了11点的时候,特性阻抗Z0的变化。

从这个图表可以看出,介电常数ε1变大,特性阻抗Z0变小。因为介电常数ε1变大,导体和参考面间的电容C变大。

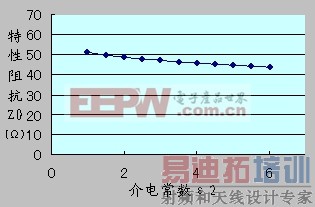

4.1.5 用图表表示介电常数ε2和特性阻抗Z0的关系

介电常数ε2在1~5范围内,以0.5间隔变化了11点的时候,特性阻抗Z0的变化。

从这个图表可以看出,介电常数ε2变大,特性阻抗Z0变小。因为介电常数ε2变大,导体和参考面间的电容C变大。

4.2 差分阻抗和各参数的关系

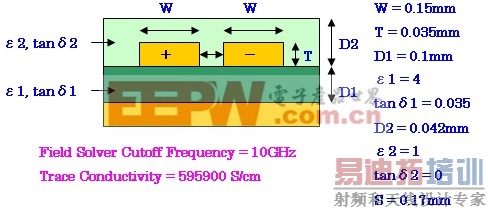

下图作为标准的层构成的时候,计算只做一个参数变化的时候,差分阻抗的变化。

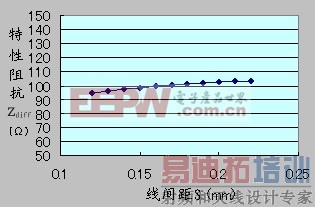

4.2.1 线间距S和差动阻抗Zdiff的关系

线间距S在0.12~0.22mm范围内,以0.01mm间隔变化了11点的时候,差分阻抗Zdiff的变化。

从这个图表可以,线间距S变大,差分阻抗Zdiff变大。因为线间距S变大,差分线路间的电容C变小。

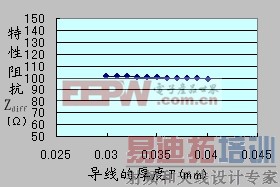

4.2.2、导线的厚度T和跟差分阻抗Zdiff的关系

导线的厚度T在0.03~0.04mm范围内,以0.001mm间隔变化了11点的时候,差分阻抗Zdiff的变化。

从这个图表可以看出,导线的厚度T变大,差分阻抗Zdiff变小。导线的厚度T变大,导体与参考面间和差分线路间的电容C及导体的电感L也变大,对差分阻抗Zdiff的影响是因为是导体和参考面间和差分线路间的电容C变大。同时,与单线比的话,差分线路间产生的电容,也使差分阻抗Zdiff也变大。

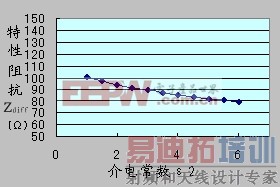

4.2.3 介电常数ε2和差分阻抗Zdiff的关系

介电常数ε2在1~5范围内,以0.5间隔使之变化了11点的时候,差分阻抗Zdiff的变化。

从这个图表可以看出,介电常数ε2变大,差分阻抗Zdiff变小。因为介电常数ε2变大,导体与参考面间和差分线路间的电容C变大。同时,与单线比的话,差分线路间上产生的电容,也使差分阻抗Zdiff变大。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...