- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的A/D转换采样控制模块的设计

摘要:本文采用FPGA器件EP1C6T144C8芯片代替单片机控制A/D转换芯片ADC0809进行采样控制,整个设计用VHDL语言描述,在QuartusⅡ平台下进行软件编程实现正确的A/D转换的工作时序控制过程,并将采样数据从二进制转化成BCD码。本设计可用于高速应用领域和实时监控方面。

关键词:FPGA;A/D转换;VHDL;采样控制;BCD码

在以往的A/D器件采样控制设计中,多数是以单片机或CPU为控制核心,虽然编程简单,控制灵活,但缺点是控制周期长,速度慢。单片机的速度极大的限制了A/D高速性能的利用,而FPGA的时钟频率可高达100MHz以上。本设计以高集成度的芯片为核心,进行时序控制、码制变换。具有开发周期短,灵活性强,通用能力好,易于开发、扩展等优点。既降低了设计难度,又加快了产品的开发周期。

1 系统设计原理

本设计采用FPGA芯片EP1C6T144C8来对ADC0809进行采样控制,并对数据进行处理,可将数据用LED显示出来。如图1所示,芯片EP1C6T144C8在对ADC0809控制时产生START转换启动信号,ALE地址锁存允许信号(高电平有效),在工作过程中,FPGA不断读入转换结束信号EOC判断AD0809转换是否结束。当EOC发出一个正脉冲时,表示A/D转换结束,此时开启输出允许OE,打开ADC0809的三态缓冲锁存器将转换好的8位二进制数输入FPGA芯片中。通过查找表的方法将8位二进制数转换成12位BCD码。

图1 控制原理图

2 FPGA模块设计与仿真

本设计采用QuartusⅡ软件平台下的VHDL硬件描述语言进行软件编程。主要分为两个部分:ADC0809的工作状态模块和二进制到BCD码转换模块。

2.1 ADC0809工作状态模块

采用双进程有限状态机的方法来实现。设计st0~st7八个工作状态。st0:初始化。st1:产生ALE的上升沿将模拟通道IN1的地址锁存。st2:产生START信号上升沿,启动A/D转换。st3:START信号延时一个脉冲。st4:A/D转换中,等待。st5:转换结束,开启输出允许信号OE。st6:OE延时一个脉冲,并开启数据锁存信号LOCK。st7:延时一个时钟,输出数据。状态转换方式见下面程序段。

case current_state is

when st0=> ale='0';start='0';oe='0';lock='0'; next_state=st1;

---初始态ST0向下一状态ST1转换,0809采样控制信号初始化;

when st1=> ale='1';start='0';oe='0';lock='0'; next_state=st2;

---由ALE的上升沿将通道地址'001'锁入0809的地址寄存器;

when st2=> ale='1';start='1';oe='0';lock='0'; next_state=st3; ---启动采样信号;

when st3=> ale='0';start='1';oe='0';lock='0';

if(eoc='0') then next_state=st4; ---转换即将结束,转换至下一状态;

else next_state=st3; ---转换未结束,继续在状态ST3中等待;

end if;

when st4=> ale='0';start='0';oe='0';lock='0';

if(eoc='1') then next_state=st5; ---EOC由0恢复1,转换结束;

else next_state=st4; ---转换未结束,等待;

end if;

when st5=> ale='0';start='0';oe='1';lock='0'; next_state=st6; --开启输出允许OE;

when st6=> ale='0';start='0';oe='1';lock='1'; next_state=st7; --开启数据锁存LOCK;

when st7=> ale='0';start='0';oe='0';lock='1'; next_state=st0;

when others=>next_state=st0; ---其它状态返回ST0;

end case;

2.2 二进制到BCD码转换模块

本设计模拟量输入范围为0~+5V,用8位二进制数表示其精度为0.02。将ADC0809输出的二进制数划分为高四位与低四位,通过查表分别算出电压值并写出对应的12位BCD码, 将得到的高四位电压与低四位电压值用12位BCD码加法,把12位BCD码分为三组,每组四位,相加从最低4位开始,且每4位相加结果超过10时需作进位动作,最终得到BCD码分别对应高、中、低三位输出显示。[p]

2.3 A/D采样控制与数据转换的部分程序及仿真

采用QuartusⅡ软件平台下的VHDL语言编程实现。

library ieee;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_1164.all;

entity ad_hgq is

port( d :in std_logic_vector(7 downto 0);---AD输入;

clk,eoc :in std_logic; ---eoc:转换结束状态信号; oe : buffer std_logic;

addr :out std_logic_vector(2 downto 0); ---oe:输出允许,addr:选通地址;

ale,start:out std_logic; ---ale:允许地址锁存;

q :buffer std_logic_vector(7 downto 0)); ---转换数据输出显示;

end ad_hgq;

architecture behaviour of ad_hgq is

type state is (st0,st1,st2,st3,st4,st5,st6,st7); ---以枚举类型定义各状态子类型;

signal current_state,next_state :state:=st0; signal regl :std_logic_vector(7 downto 0);

signal addrx :std_logic_vector(2 downto 0):=000;

signal lock :std_logic; ---转换后数据输出锁存时钟信号;

signal hex :std_logic_vector(7 downto 0);

begin

process(clk)

begin

if(clk'event and clk='1') then current_state=next_state;

end if; ---在时钟上升沿,转换至下一状态;

end process ; ---由信号current_state将当前状态带出进程,进入下一进程;

process(lock)

begin

if lock='1'and lock'event then regl=d;

end if; --在lock上升沿,将转换好的数据锁存入8位锁存器中;

end process;

process(clk)

begin

if clk'event and clk='1' then

if current_state=st0 then addrx=addrx+1; ---进入下一地址通道;

end if;

end if;

addr=addrx;

end process;

q=regl; ---数据输出;

process(clk)

begin

if( clk'event and clk ='1') then if oe='1' then hex=q; ---将数据送给hex;

end if;

end if;

end process;

end behaviour;

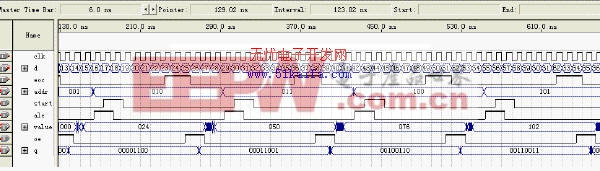

图2显示的是A/D采样控制并将所采的数据转换为BCD码的仿真结果。图中Value为所采的电压结果值。

图2 采样控制模块仿真

3 结束语

采用EP1C6T144C8芯片实现对A/D转换器的采样控制,充分利用了FPGA的高速度和高可靠性,从而解决了传统中用单片机控制时速度慢的问题。FPGA具有灵活的编程方式,简单方便的编程环境,易学易用,大大提高工作效率,缩短研制周期。本设计可用于高速应用领域和实时监控方面。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...