- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

用 FPGA 产生高斯白噪声序列的一种快速方法

0 引言

短波信道存在多径时延、多普勒频移和扩散、高斯白噪声干扰等复杂现象。为了测试短波通信设备的性能,通常需要进行大量的外场实验。相比之下,信道模拟器能够在实验室环境下进行类似的性能测试,而且测试费用少、可重复性强,可以缩短设备的研制周期。所以自行研制信道模拟器十分必要。

信道模拟器可选用比较有代表性的 Watterson 信道模型 ( 即高斯散射增益抽头延迟线模型 ) ,其中一个重要环节就是快速产生高斯白噪声序列,便于在添加多普勒扩展和高斯白噪声影响时使用。传统的高斯白噪声发生器是在微处理器和 DSP 软件系统上实现的,其仿真速度比硬件仿真器慢的多。因此,选取 FPGA 硬件平台设计高斯白噪声发生器可以实现全数字化处理,同时测试费用少、可重复性强、实时性好、速度快,能较好地满足实验需求。

本文提出了一种基于 FPGA 的高斯白噪声序列的快速产生方案。该方案根据均匀分布和高斯分布之间的映射关系,采用适合在 FPGA 中实现的折线逼近法。该方法实现简单,快速且占用的硬件资源少,而且采用 VHDL 语言编写,可移植性强,并可灵活地嵌入调制解调器中使用。

1 均匀分布随机数发生

1.1 m 序列发生器

伪随机噪声具有类似随机噪声的一些统计特性,且便于重复产生和处理,因此获得了广泛的应用。 m 序列就是一种常用的伪随机序列,该序列又被称作最长线性反馈移存序列。 m 序列是由线性反馈移位寄存器产生的周期最长的一种序列。如果选用 n 级线性反馈移位寄存器,则 m 序列的周期为 (2n-1) 。对于 m 序列来说,将 n 级线性反馈移位寄存器状态看成无符号整数,则状态的取值范围为 1 ~ (2n-1) ,并且在 m 序列的一个周期内,移位寄存器的每种状态都会出现且只出现一次,但要注意线性反馈移位寄存器的初始状态设定为非零值,并且在给定任意非零初始状态时, m 序列的周期都不变。显然,移位寄存器的状态值是服从均匀分布随机数。制作 m 序列发生器时,线性反馈移位寄存器的反馈线连接情况可通过查找本原多项式来得到 ( 系数为 1 表示对应位有反馈线连接,为 0 表示对应位无反馈线连接 ) 。所以,线性反馈移位寄存器反馈线的数目以及模 2 加法器的数目直接决定于本原多项式的项数。为降低硬件资源的消耗,设计时可选取项数少的本原多项式。为了使伪随机序列的周期足够长以满足设计要求,采用的本原多项式为: x18+x7+1 ,即用一个 18 级线性反馈移位寄存器就可产生周期为 (218-1) 的 m 序列。其连线如图 1 所示。

1.2 降低相关性模块

[p]

高斯白噪声信号是一个随机过程,每个样值点都是一个高斯变量,其双边功率谱密度为常数 N0 / 2 ,即:

由 (2) 式可见,高斯白噪声在任意两个不同时刻的采样信号是统计独立的。但是,从 m 序列的产生过程可见,每个时钟周期中,线性反馈移位寄存器只移出一个最高位,并反馈一个值给最低位,所以,相邻的几个状态之间不是完全独立的。这必然影响高斯白噪声任意两个不同时刻采样信号之间的独立性。所以要进行非相关性操作。为了减小相关性,通常的方法是产生高斯序列后再接一个交织器,把高斯序列出现的前后顺序打乱。但建交织器要占用 FPGA 的硬件资源,所以,本设计不采用交织器。

考虑到 m 序列的周期为 (2n-1) ,第 2n 个值往后都是不断重复第 1 个到第 (2n-1) 个状态。所以只要线性反馈移位寄存器每隔 r 个同步时钟 ( 其中 r=2i , i 为整数 ) 输出一个状态值 ( 即线性反馈移位寄存器每变换 r 个状态输出一次状态值 ) ,就能在不改变 m 序列原有周期的情况下减小相关性,且不增加硬件资源的消耗。但要注意: r 一定要是 2 的幂,这样才能保证 m 序列的周期不变。

2 均匀分布向高斯分布的转换

2.1 均匀分布和高斯分布之间的映射关系

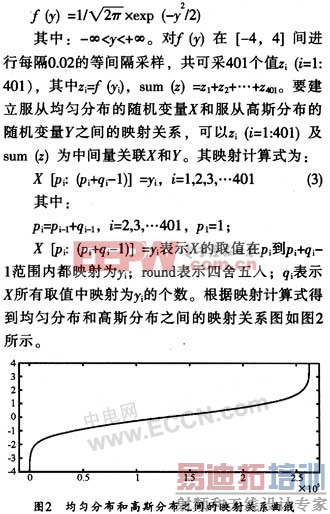

设 X 服从 [1 , 218-1] 区间内的均匀分布; Y 服从均值为 0 、方差为 1 的标准正态分布,那么,考虑到高斯分布的实际情况, Y 仅在 [-4 , 4] 之间取值即可。 Y 的概率密度函数为:

2.2 折线逼近法

[p]

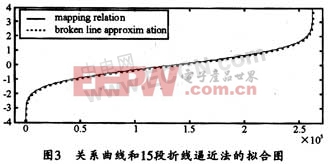

如果直接应用上述映射关系进行均匀分布向高斯分布的转换,则需开辟 (218-1) 个物理空间来建立查找表,这几乎不可能实现。但由图 2 可见,其关系曲线在很大区间上表现出线性关系,所以,可以以斜率不同的直线段分段逼近关系曲线。在一定精度要求下,该方法简单易行,占用硬件资源少,适合在 FPGA 中实现,从而实现由服从均匀分布向服从高斯分布的快速转换。图 3 是关系曲线 ( 实线 ) 和 15 段折线逼近法 ( 虚线 ) 的拟合图,由图可见,其实线和虚线拟合得很好,从而证明了折线逼近法能较好的反映映射关系。

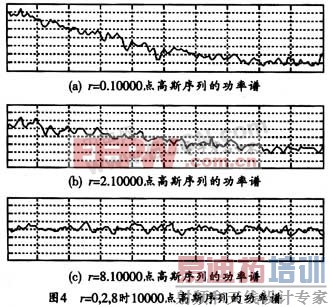

利用 m 序列的周期特性可降低高斯白噪声任意两个不同时刻的采样信号的相关性。在线性反馈移位寄存器中每隔 r 个同步时钟 ( 其中 r=2i , i 为整数 ) 输出一个状态值作为均匀分布的随机数输入可实现均匀分布向高斯分布的转化。为了选择合适的 r 值,图 4 分别给出了 r 为 0 、 2 、 8 时所生成的 10000 点高斯序列的功率谱。由图 4 可见, r=8 时的功率谱基本水平,即系统产生的高斯白噪声任意两个不同时刻的采样信号可看成统计独立的,这与理论上对高斯白噪声的定义相一致。同时也证明了降低相关性模块是可行和有效的。

3 硬件实现

在 ISE8.1i 开发环境中使用 VHDL 语言可实现上述高斯白噪声发生器的功能。本设计选用 Xil-inx 的 xc3s1200e-4fg320 作为目标器件。其硬件实现框图如图 5 所示。

产生高斯白噪声先后通过两个模块来实现。一是均匀随机数发生模块;二是均匀分布向高斯分布转化模块。其中均匀随机数发生模块包括 m 序列发生器和非相关化处理 ( 降低相关性操作 ) ;均匀分布向高斯分布转化模块包括比较选择器、相应的延时操作以及算术计算模块。

[p]

[p]

在 ISE8.1i 开发环境中得到的系统功能仿真图如图 6 所示。实验中,系统的输入时钟为 60MHz 。图 6 中的 regl_value 表示线性反馈的移位寄存器在时钟 clk1 上升沿触发的状态值。 reg2_value 表示在同步时钟 clk2 上升沿采样 reg_value1 的值, clk2 是 clk1 的 8 倍分频。仿真证明,本系统可以实现线性反馈移位寄存器每转 8 次取出一个状态值,并可减小不同时刻随机变量之间的相关性 ( 非相关化处理 ) 。根据 reg2_value 并通过比较选择器输出对应直线段的 slope( 斜率 ) 、 point( 起点的横坐标 ) 、 point_value( 起点的纵坐标 ) 可见, reg2_value_delay 比 reg2_value 可延时半个 clk2 ,因而可保证输入算术计算模块的数据的同步。这样,再经算式: gauss_output=(reg2_value_delay-point)*slope+point_value ,就可得到高斯白噪声序列。为了确保采得稳定的信号值,操作时应在信号持续时间的中间位置进行采样。由于高斯白噪声序列 gauss_output 是 reg2_value_delay ,、 point 、 slope 、 point_value 之间的加、减、乘运算所得到的,所以, gauss_output 有相应延时。

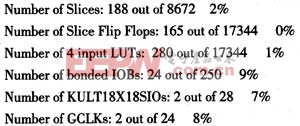

本设计用 Xilinx 的 xc3s1200e-4fg320 为目标器件来对代码进行综合,所用的 FPGA 资源如下:

可见,该方案占用硬件资源较少。

为了验证硬件实现的正确性,还可将其下载到开发板,并采用 ChipScope Pro 8.1i 将硬件产生的高斯白噪声序列通过并口回传,同时将数据导入到 Matlab 。由于 ChipScope 要利用 FPGA 的片内存储空间暂存采样值,所以,一次采集的信号数目有限且与 FPGA 型号有关。笔者将一次采集到的 16384 个样值导入 Maflab 后,再将数据小数化 ( 因为 FPGA 中处理的是定点数 ) ,然后调用 Matlab 中的 psd 函数估计出了其功率谱图。实际结果证明,本系统产生的高斯白噪声与理论值非常接近,也就是说,该方案可行。

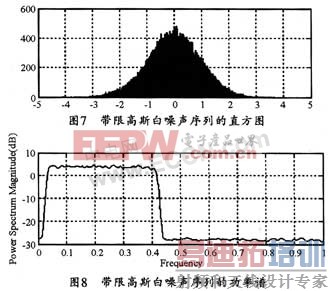

由于本系统采用 VHDL 语言编写,故其可移植性较强。当在通信工程中需要带限高斯白噪声时,就可在高斯白噪声后接一个带通滤波器 ( 在 FPGA 中应用自带 IP 核可轻松实现 ) 。由于滤波后的噪声能量会有损失,所以要做相应的能量补偿。之后,再将产生的带限高斯白噪声序列 ( 约 50000 点 ) 导入 Matlab 中,然后调用 hist 函数就可得到图 7 所示的序列直方图,而调用 psd 函数即可得到图 8 所示的序列功率谱图。从直方图可见带限高斯白噪声的概率密度函数是高斯型的,而从功率谱可见,在通带内,功率谱密度近似为常数,这些都与理论一致。

4 结束语

本文提出了一种在 FPGA 中快速产生高斯白噪声序列的实现方案。同时基于均匀分布和高斯分布之间的映射关系曲线,提出并应用了适合在 FPGA 中实现的折线逼近法。本文采用了 15 条首尾连接的直线段去逼近映射关系曲线 ( 按不同的工程精度要求,可选择个数不同的直线段去逼近 ) 。显然,所用的折线拐角越多 ( 直线段个数越多 ) ,精度越高,但所消耗的 FPGA 资源也越多。该方案具有简单易行,运算量小等优点。而且实现速度快,可源源不断的产生高斯白噪声序列,同时占用的硬件资源较少。由于软件采用 VHDL 语言编写,可移植性强,故可灵活用于 Watterson 信道模拟器或嵌入调制解调器等其它系统。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...