- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于PCI总线和CPLD的任意信号发生器设计

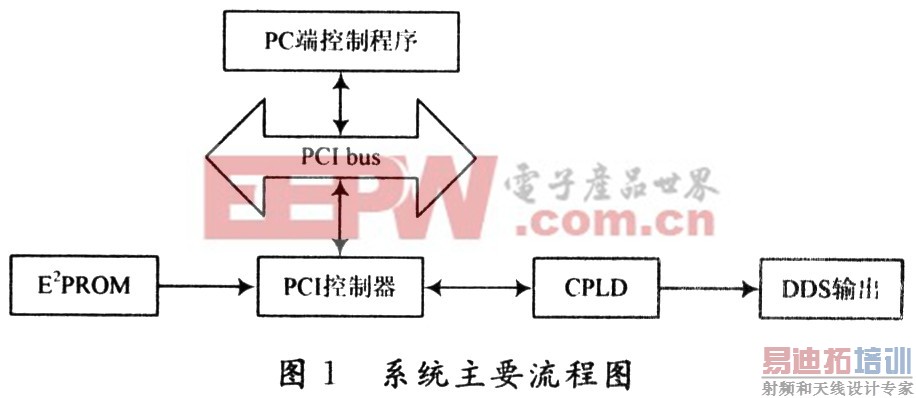

2 系统主要硬件设计

2.1 PCI总线接口部分设计

PCI总线作为计算机与外部设备的一个重要连接总线,数据传输稳定、灵活、传输速度快,还具有即插即用和良好的扩展性等优点,被广泛应用在各种与计算机互联的设备中。

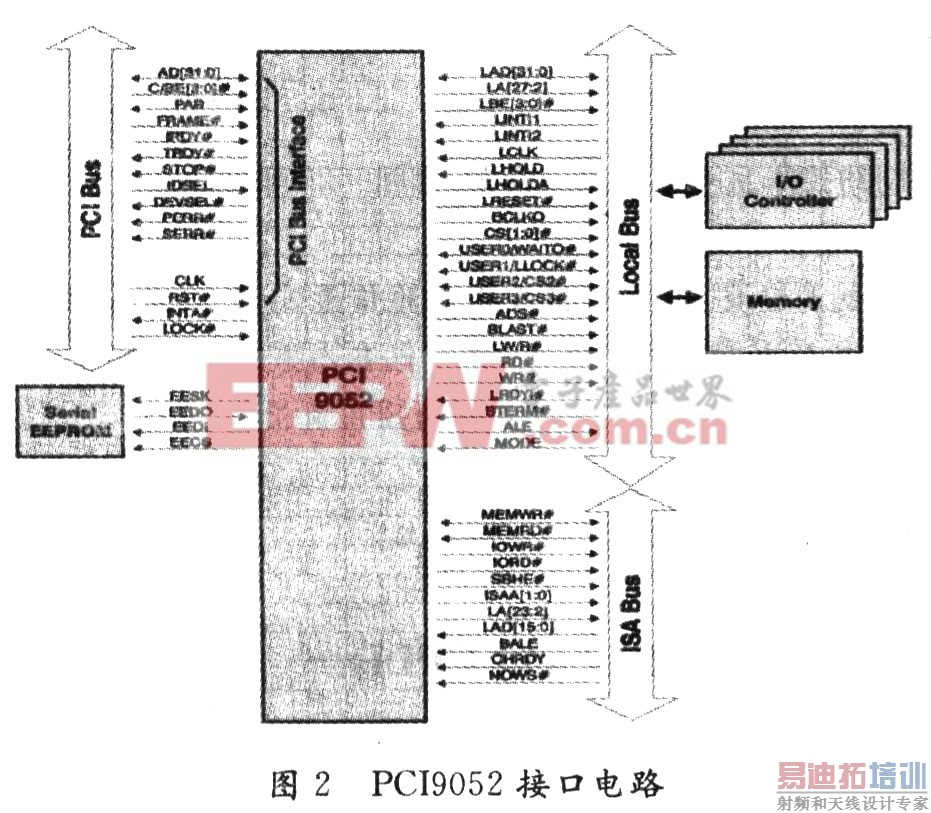

考虑到PCI总线的协议比较复杂,所以本设计采用了PLX公司生产的PCI接口专用芯片PCI9052用于PCI总线的控制。图2是PCI9052芯片的主要接口电路图。主要包括9052与PCI插槽间的连接信号线、与E2PROM之间的连接线和与局部总线之间的连接线。与PCI插槽的信号包括地址数据复用信号AD[31:O].总线命令信号C/BE[3:0]#和PCI协议控制信号PAR,FRAME#,IRDY#,TRDY#,STOP#,IDSEL,DEVSEL#,PERR#,SERR#。与串行E2PROM的连线有4根信号线:EESK,EEDO,EEDI和EECS。本设计中需要传输的数据量比较少,同时考虑到对早期的ISA设备的兼容性,所以采用了9052中的ISA模式。在ISA模式下,9052与ISA总线的连接有数据线LAD[7:0],地址线ISAA[1:O],LA[23:2],I/O读写信号线IOWR#,IORD#,地址锁存BALE。

9052的工作方式及配置信息主要由E2PROM加载,这里采用了Motorola公司的93LC46B,E2PROM的数据可以提前用烧写器烧好,也可以在线烧写。配置信息包括:设备号DID、制造商号VID、子设备号SDID、子制造商号SVID、中断号、设备类型号、局部空间基地址、局部空间描述符、工作模式、LOCAL端数据线的宽度、片选以及局部响应控制CNTRL等信号。根据需要配置好这些信息,写入E2PROM中。本设计中E2PROM的配置信息如表1所示。

2.2 CPLD控制部分设计[p]

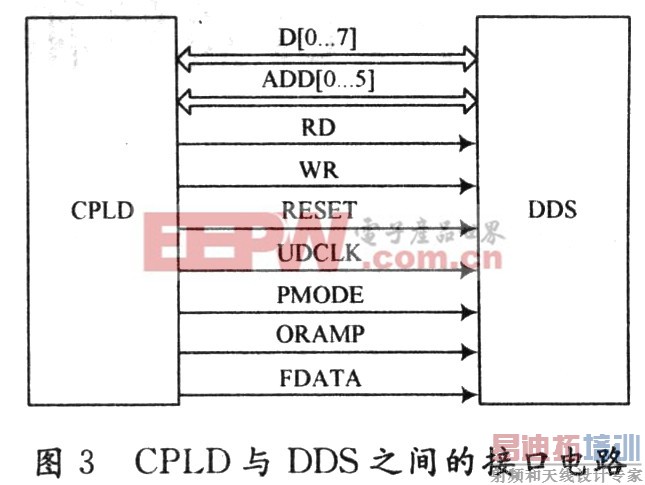

CPLD在系统中的主要作用是用来将PCI控制器传输过来的数据,经过一定的算法处理,得到DDS外围管脚的状态及向DDS中写入控制寄存器数值,使DDS根据配置信息产生所需要的信号。

本设计中使用的CPLD是Altera公司的7000S系列,工作电压为5 V,具有192个宏单元,采用通用JTAG方式下载。CPLD与DDS之间的接口电路主要包括8位数据线D[7:O]。6位地址线ADD[5:0],串并选择信号PMODE,复位信号RESET,外部更新信号UDCLK、读写信号WR、RD和控制信号0RAMP、FDATA。如图3所示。

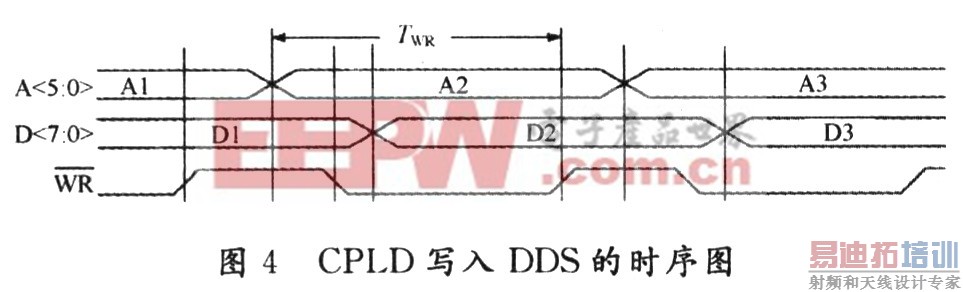

考虑到DDS信号输出的实时性和减少CPLD的宏单元的占用,本设计中使用9052的IOWR#信号去触发DDS的写入信号WR。DDS控制寄存器的写入方式有串行和并行两种,由PMODE管脚控制,当PMODE信号为高时,为并行写入模式,当PMODE信号为低时,为串行工作模式。由于设计中PCI9052写入CPLD的数据为8位并行输入,所以在这里选用了并行的方式向DDS的控制寄存器中写入数据。写入的时序如图4所示。

CPLD的程序在Altera公司提供的QuartusⅡ开发系统下通过Verilog HDL语言来实现。在QuartusⅡ环境中,可以方便地对波形进行仿真,便于查看和修改程序中可能存在的问题。QuartusⅡ仿真环境如图5所示。

2.3 DDS输出部分设计

DDS部分电路设计除了与CPLD之间的连接电路外,还有DDS的外围电路设计。本系统中DDS的外围电路主要包括电压转换、差分时钟信号输入和低通滤波器三个部分,如图6所示。设计中的DDS采用的是AD公司的通用DDS芯片AD9852,芯片的工作电压为3.3 V,最高系统时钟为300 MHz。

在整个系统中,PCI9052和CPLD的工作电压为5 V,所以需要将工作电压由5 V转换为DDS正常工作的3.3 V,设计中采用了专用的电压转换模块,完成电压转换工作,为DDS及其外围电路提供3.3 V工作电压。

差分时钟输入模块是为了DDS输出信号能够得到较好频谱纯净度,本设计采用了20 MHz的有源晶振,通过MCl00LVEL16D芯片产生20 MHz的差分时钟信号,作为DDS的外部输入时钟。

为了滤去不需要的频率成分和抑制输出信号的杂散,在信号的输出部分,采用了一个π型结构的LC低通滤波器,滤波器的结构图如图7所示。[p]

3 系统主要软件设计

系统的软件部分包括面向硬件的WDM驱动程序和面向用户的应用程序两部分,其结构如图8所示。WDM驱动负责硬件的电源管理、各种空间访问和初始化等硬件控制操作。用户通过应用程序与驱动程序通信、与PC机进行数据交换,传递所需参数和控制信息,再通过信号生成部分根据设置的参数产生所需要的各种信号。

本设计的软件部分开发环境为:Windows XP,WinXPDDK,MS.Net Framework SDK,DriverStudio 3.3,Win―driver5.02,VC++6.O。根据9852的工作特性,用户软件中设置了信号种类选择、信号的频率、分频系数等参数的设置,还可以根据以后更进一步的需要,产生其他需要的各种实际信号,编译完成的软件如图9所示。实际产生的信号如图10所示。

4 结语

本文详细介绍了基于PCI总线和CPLD的任意信号发生器的开发过程,并对其中的关键技术,如PCI总线控制、CPLD逻辑控制、DDS信号输出部分、控制软件的编写等主要部分做出分析和研究。提出了基于用户软件控制信号产生的任意信号发生器的设计思路并加以实现。通过频谱仪观察实际的输出信号,信号的频谱比较纯净,信号的样式多样,参数设置直观方便。同时提供了一个通用的软件平台,可以根据以后的实际需要进行相关功能的扩展,以得到更多的信号样式和一些非常规信号。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...