- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的高速数据采集存储系统的设计

0 引言

信息技术的发展,特别是各种数字处理器件处理速度的提高,实时处理大量的数据已经成为现实。但是,在一些恶劣环境和数据无法进行实时传输的情况下,还必须用到存储测试的方法。存储测试是指在对被测对象无影响或影响在允许的范围条件下,在被测体内置入微型存储测试系统,现场实时完成信息快速采集与存储,事后对存储器进行回收,由计算机处理和再现被测信息的一种动态测试技术。针对具体的情况,我们研制开发了一种用蓄电池就可工作的、能在各种恶劣环境下应用的、可回收的小体积低功耗的大容量数据采集存储系统。

1 系统总体设计

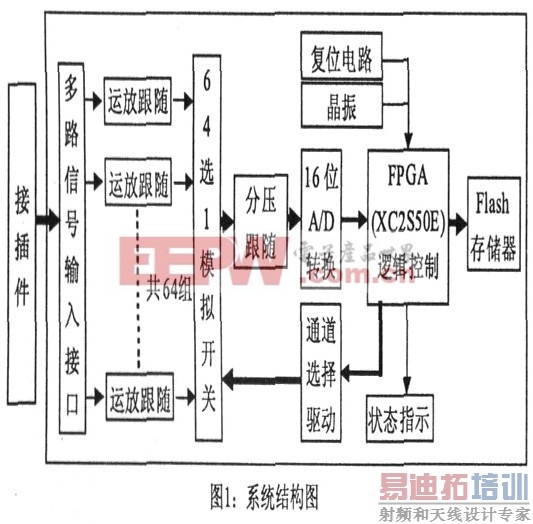

整个系统以FPGA为核心控制器来组织工作,它控制着整个系统的读、写、擦除等操作。系统主要解决的问题是采集、存储和数据事后读取。系统整体框图如下图1所示。

1.1 数据采集

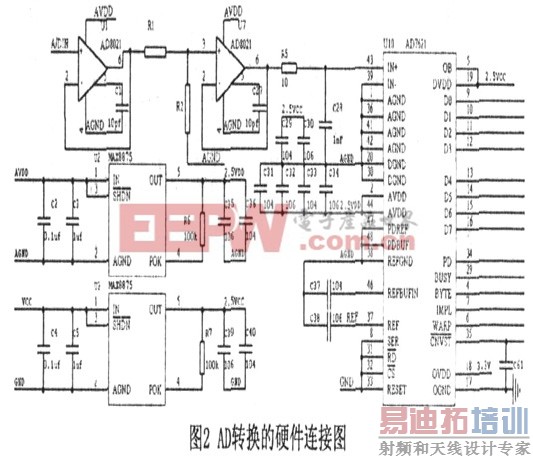

由于要同时对多路信号进行采集,我们采取了FPGA对模拟开关进行均等时间推进以实现通道的转换。当转换到某一通道时,FPGA同时要启动A/D进行模数转换。为了达到高精度采集的目的,采用16位的AD转换器AD762l,模拟开关选用ADG706。以下是AD转换器的硬件电路连接图2。

1.2 AD采集时序

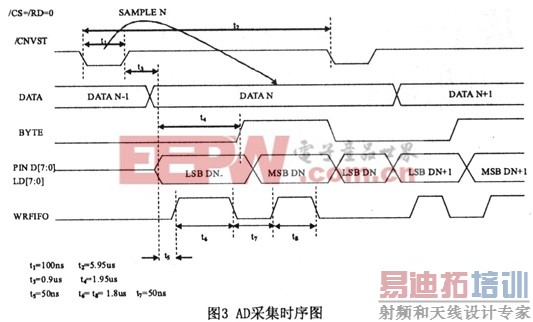

AD采集时序图如下图3所示。AD采集过程从/CNVST信号下降沿开始,BUSY信号下降沿完成,BYTE信号控制数据类型,低电平为低8位数据,高电平为高8位数据。延迟0.9us给出第一个WRFIFO信号,WRFIF0高电平有效,在此期间数据线上的数据为低8位数据,经过1.8us的低电平后,给出第二个WRCLK信号,此时数据为高8位数据,一个数据的转换完成。图3 AD采集时序图

1.3 数据存储

对数据的存储,我们采用闪存(FLASH Memory)作为存储器.它具有体积小、功耗低和数据不易丢失的特点。对FLASH的写操作过程有其固定的操作模式,如图3所示。由于FLASH是按页存储的,当一页写完之后要进行下一页的控制字和地址的重新写入,为了使采集回来的数据能及时准确的写/kFLASH,而不至于在页与页的交替时间内使数据丢失.所以不可能将采集回的数据直接存入FLASH,我们利用FPGA内部集成FIF0来缓存FLASH MEMORY编程期间A/D控制器上传的数据,A/D转换器总的采样率为12KSPS,精度为12位,加上通道号和帧计数,每秒钟A/D控制器上传到FIF0的数据为34KB。FLASH MEMORY最大编程时间为300us。在FLASH MEMORY编程期间A/D转换器上传到FIF0的数据为:34KB×300us=10.2B。因此FPGA内部集成FIF0设计成宽度为一个字节,深度为1024的异步FIFO,即总容量为1KB,完全能够缓存FLASH MEMORY编程期间A/D控制器上传的数据。[p]

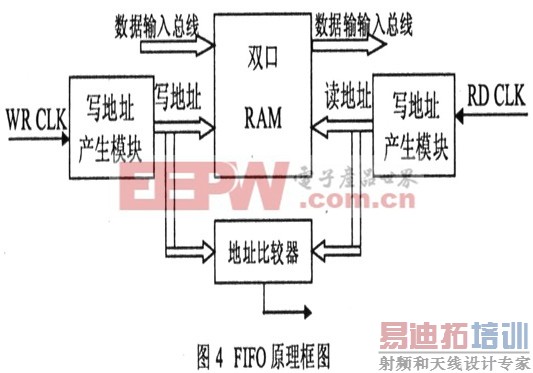

FPGA内部集成FIFO是由存储器、地址比较器、写地址控制器和读地址控制器构成,原理框图如4所示。

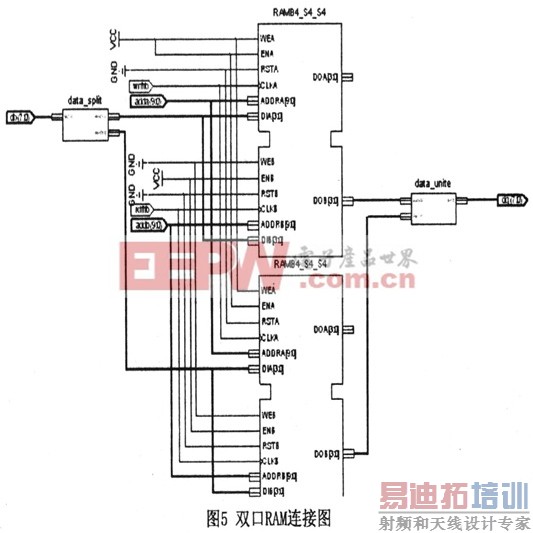

其中存储器是由两个宽度为4位、深度为1024的双口RAM采用并联的方式构成的。连接方法如图5所示。

通过DIA端口将数据写入双口RAM,通过DOB端口将数据读出,WEA和JENA接VCC,即接高电平,使双口RAM的A部分工作在写入状态,在CLKA的上升沿通过DIA将数据写入双口RAM;WEB接GND,即接低电平;ENB接VCC,即接高电平,使双口RAM的B部分工作在输出状态,在CLKB的上升沿通过DOB将数据输出双口RAM。

1.4 数据的分区存储

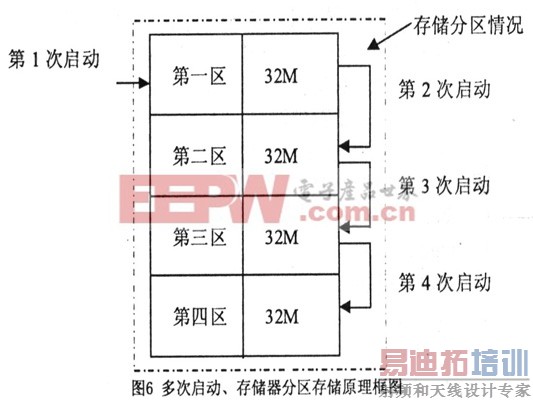

本系统采用一片FLASH存储器,该芯片有128M Byte的容量,根据计算32M Byte的容量就可以把需要采集的数据全部记录下来,所以把存储器按其块地址顺序分为4个区,每个区均为32M Byte。测试系统上电复位后首先进入的是自检状态,每次顺序检测第1区中是否有数据,如果没有则把该次启动的采集的数据顺序写入第l区中,直到第1区存储完成,则停止记录并且系统断电。断电后再一次启动采集也一样首先检测第一块中是否有数据,有数据则检测下一块是否有数据,若没有数据,则顺序把从FIFO中上传的导弹飞行数据写入存储器,如果有数据,则依次地址跳到下下一块,采集满则停止,依次类推,直到把4个区都写入了数据,则不论怎么启动采集也不会把数据覆盖再写入,除非执行擦除操作把存储器中的数据清空。

这种多次启动系统,存储器分区记录的技术使系统具有一定的冗余设计,虽然不能从根本上消除误启动而造成整个试验的失败,但是该技术在实际试验中具有十分重大的意义。

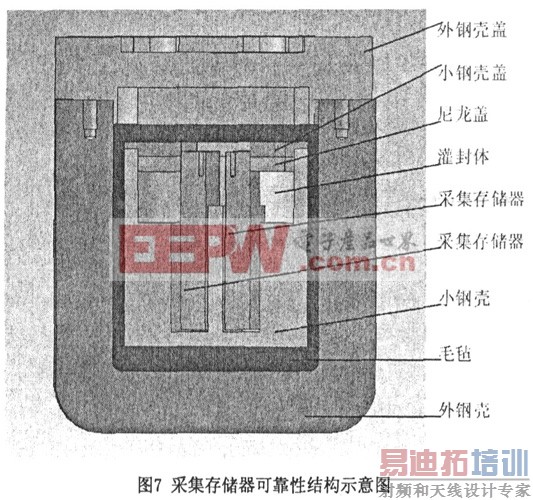

2 系统的灌封技术

采集存储系统需工作在高温高压等恶劣环境下,因此最重要的是它的防护结构的设计。在结构设计上采用了抗高冲击的结构设计技术,主要包括:缓冲保护技术、灌封保护技术,力求能够最好的保护好存储模块。图7是采集存储器的可靠性结构示意图。图7采集存储器可靠性结构示意图

3 创新性说明

本文介绍了一种基于FPGA的多路数据采集存储系统的设计方法及其可靠性结构设计,该系统存储容量大,体积小,可工作在高温、高压、强冲击、强振动、高过载等恶劣环境下。采用了存储器分区存储技术,可以避免误操作将有用数据覆盖。该系统已投入使用,性能优,值得推广。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:稳健参数设计的新方法

下一篇:基于EP1C3T144C8的FPGA的开发板设计