- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的电子琴动态录音与回放系统的设计

O 引 言

乐曲都是由一连串的音符组成,因此按照乐曲的乐谱依次输出这些音符所对应的频率,就可以在扬声器上连续地发出各个音符的音调。大多数的电子琴设计都有弹奏和播放功能,但能自动对弹奏的乐曲进行录音并可改变回放快慢可调的设计却很少。要实现录音和回放功能,就必须将弹奏的音符值在相应的写控制信号控制下存储到FPGA芯片内部的随机存储器(RAM)中,而在相应的读控制信号控制下,将RAM中存储的音符值读出来,送给相应的发声控制等模块。进入20世纪90年代以后,EDA技术得到了飞速的发展,电子系统的设计方法发生了很大的变化,传统的设计方法正逐步退出历史舞台,而基于EDA技术的可编程逻辑芯片设计成为电子系统设计的主流。本设计基于QuartusⅡ6.0开发平台,采用VHDL语言在FPGA芯片上成功地实现了电子琴动态录音与回放功能。

l 电子琴动态录音与回放系统设计

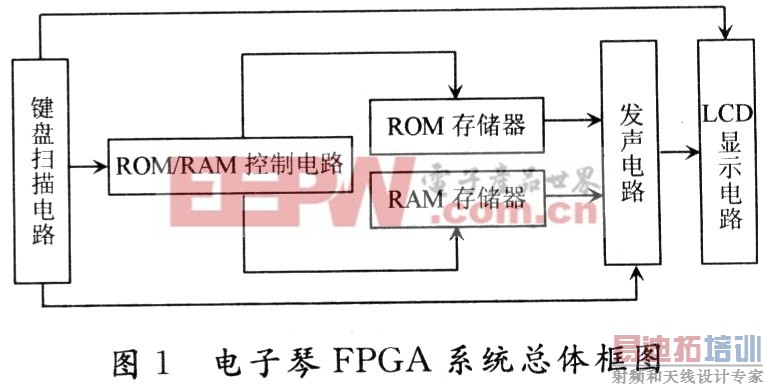

已经设计成功的多功能电子琴乐曲硬件演奏设计电路主要包括:键盘演奏、人工选曲并播放乐曲、录音/回放、可控制播放歌曲的节奏快慢、液晶显示当前系统状态等功能。其中在FPGA芯片中实现的电路设计有4个模块,分别为键盘扫描和按键功能设置模块、RoM/RAM控制器模块、发声控制模块、LCD驱动控制模块。系统设计框图如图1所示。

工作原理如下:首先通过键盘扫描和按键功能设置模块将一个4*4的键盘上各按键进行功能设置,然后根据相应的操作要求进行发声和液晶显示。如果选中当前状态是弹奏模式,则发声控制模块直接把琴键送来的音符对应的分频系数转换成相应频率送到扬声器发声,字幕信息通过液晶显示驱动模块驱动液晶显示;如果选中当前工作模式为播放模式,则ROM/RAM控制器模块把事先存储在ROM中的音乐数据提出来送至发声模块,完成自动播放功能;如果选中当前工作状态是录音回放模式,则启动ROM/RAM控制器模块中RAM状态机控制器进行读写操作。

这里重点介绍由ROM/RAM控制模块通过状态机设计产生录音/回放功能的实现。

2 ROM/RAM控制模块的设计

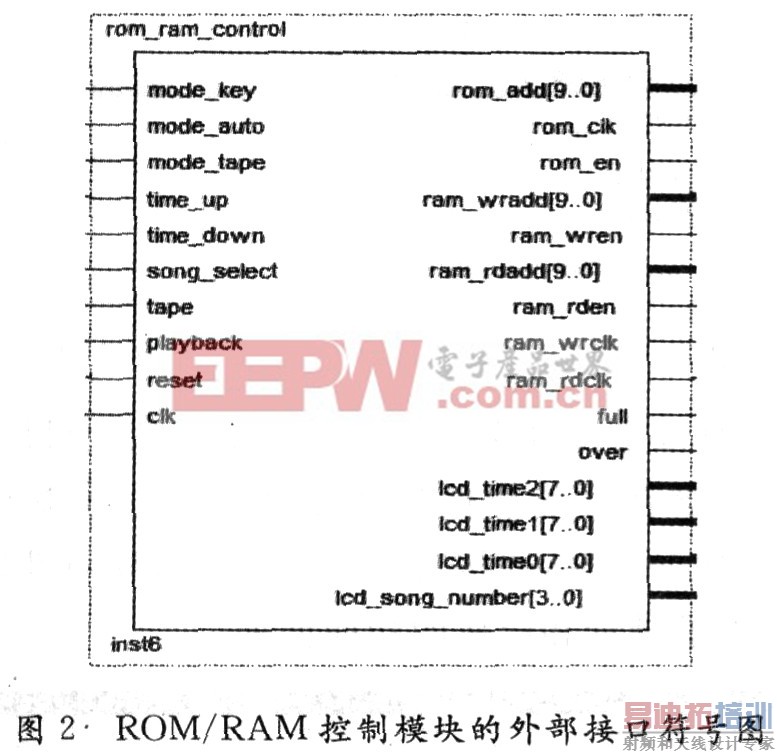

ROM/RAM控制模块的作用是通过对系统当前所处的模式进行判断,并根据输入的控制信号,对CycloneⅡFPGA内嵌的RAM的读写信号、读写时钟及读写地址进行控制。其中ROM/RAM控制模块的外部接口符号图如图2所示。

此模块定义了10个输入端口,分别为:mode_key(键盘演奏模式)、mode_auto(播放歌曲模式)、mode_tape(录音回放模式)、time_up(节奏上升)、time_down(节奏下降)、song_select(曲目选择)、tape(录音)、playback(放音)、reset(系统复位)、clk(时钟)。定义了15个输出端口:rom_add(ROM地址)、rom_clk(ROM时钟)、rom_en(ROM时钟使能)、ram_wradd(RAM写地址)、ram_wren(RAM写使能)、ram_wrclk(RAM写时钟)、ram_rdadd(RAM读地址)、ram_rden(RAM读地址)、ram_rdclk(RAM读地址)、full(录音满信号)、over(回放完毕信号)以及5个提供LCD驱动显示用的信号。

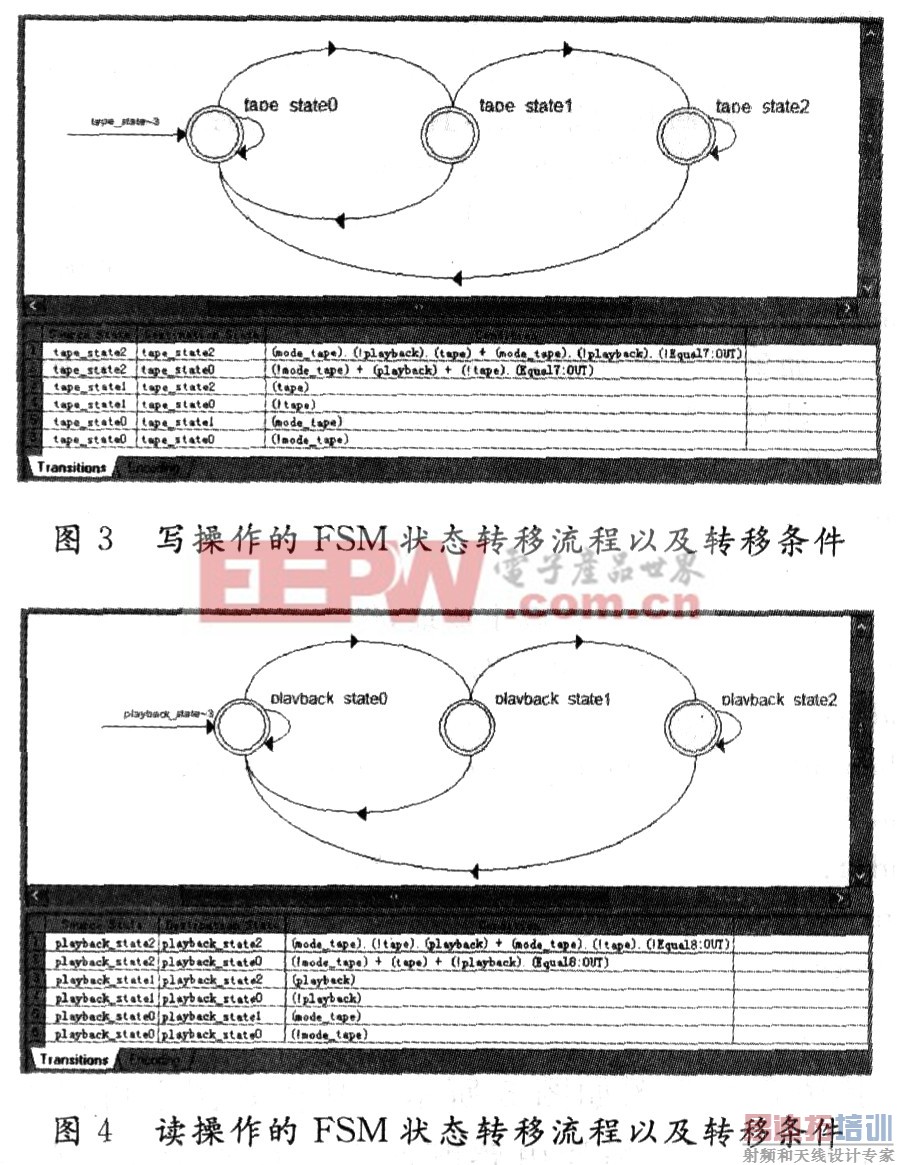

RAM/ROM控制模块中的RAM控制部分分成两个小部分,采用有限状态机(FSM)分别对RAM读状态和RAM写状态进行操作控制。当系统当前模式为“录音/回放模式”时,如果“录音”按键按下,则RAM进行写操作,从首地址开始进行存储。如果存储满1 024个地址空间,则提示“录音满”,写操作终止,等待用户命令,以进行下一步操作。当系统当前模式为“录音/回放模式”时,如果“回放”按键按下,则RAM进行读操作,从首地址开始将RAM单元中的数据送给发声控制模块进行播放。如果读完1 024个地址空间,则提示“回放完毕”,读操作终止,等待用户命令,以进行下一步操作。[p]

写操作的FSM状态转移流程以及转移条件如图3所示;读操作的FSM状态转移流程以及转移条件如图4所示。

用状态机对RAM进行读写控制的部分源程序如下:

其仿真波形图如图5所示。从仿真图上可以看出,RAM/ROM控制模块电路既产生了控制RAM存储器的时钟ram_wrclk信号,也产生了相应的控制RAM的使用使能信号ram_wren和写入地址ram_wradd。

3 RAM随机存储器的设计[p]

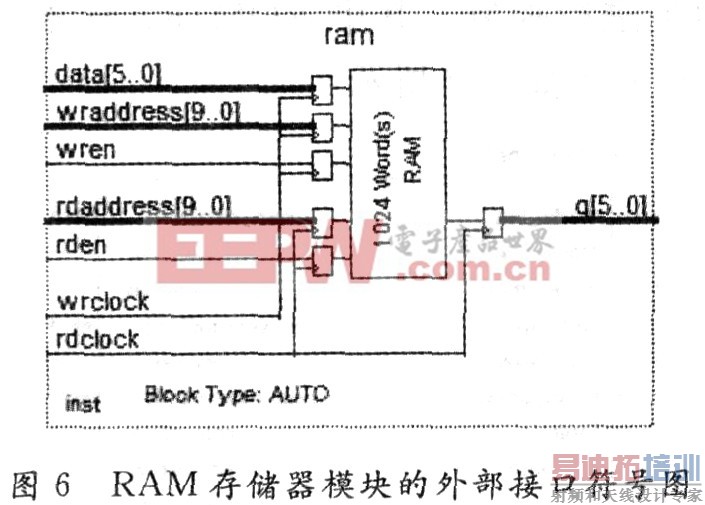

设计一个双端口的存储深度为1 024、存储宽度为6位的随机存储器RAM,用来存储弹奏的乐曲,并可播放出来。生成的RAM单元如图6所示。data[5..O]端口为弹奏电子琴时由发声控制模块产生的音符数据。

当系统处于“录音/回放模式”的“录音”状态时,将当前所弹奏的音符进行转换,输出作为RAM的存储数据“DATA”。wraddress[9..O]代表十位宽度的写地址端口,rdaddress[9..0]代表十位宽度的读地址端口。wrclock为RAM写入时钟,rdclock为RAM读出时钟。Q[5..0]为从RAM中读出所存放数据,即data。从图6可以看出,此双口RAM具有独立的读写时钟和读写使能。选择这样的RAM的目的是为了以一个固定频率wrclock(本设计取4 Hz)的时钟对RAM进行写操作,即以一个固定的采样频率对所弹奏的乐曲进行采样存储;另一方面以节奏控制部分输出的时钟rdclock作为RAM的读时钟信号,使得回放过程可以以不同的节奏将储存的乐曲播放出来。这是其新颖之处,使电子琴在回放过程中更加灵活多变,功能更多。

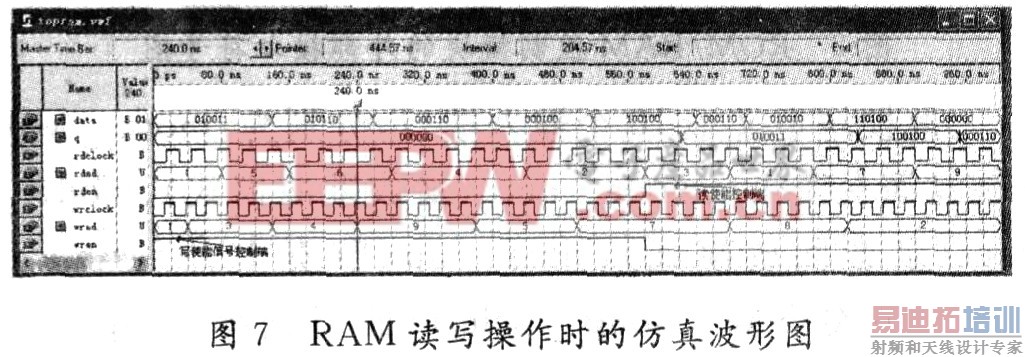

其仿真波形图如图7所示。从仿真图上可以看出,RAM存储器在写使能信号和读使能信号控制作用下依次写入数据信号,并按写入地址先后次序再准确地读出来,实现了录音和回放的功能要求。

本设计采用杭州康芯电子有限公司开发的电子设计应用板(型号:KX―DVP3F)进行对系统的调试与功能验证。利用QuartusⅡ6.O软件生成.sol或者.pof编程文件,通过USB下载器将编程文件配置到CycloneⅡEP2C8Q208芯片中,经过数次的调试,多功能电子琴的全部技术指标和功能很好地符合设计要求,发声准确,易操作,可视性强。

有限状态机设计技术是实用数字系统中的重要组成部分,也是实现高效率高可靠逻辑控制的重要途径。它具有类似CPU的高速运算和控制能力,程序层次分明,结构清晰,易读易懂;在排错、修改和模块移植方面也有独到之处。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...