- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的UART模块的设计

0 引 言

在计算机的数据通信中,外设一般不能与计算机直接相连,它们之间的信息交换主要存在以下问题:

(1)速度不匹配。外设的工作速度和计算机的工作速度不一样,而且外设之间的工作速度差异也比较大。

(2)数据格式不匹配。不同的外设在进行信息存储和处理时的数据格式可能不同,例如最基本的数据格式可分为并行数据和串行数据。

(3)信息类型不匹配。不同的外设可能采用不同类型的型号,有些是模拟信号,有些是数字信号,因此采用的处理方式也不同。

为了解决外设和计算机之间的信息交换问题,即需要设计一个信息交换的中间环节――接口。UART控制器是最常用的接口。

通用异步收发器(Universal Asynchronotls Receiv―er/Transmitter,UART)是辅助计算机与串行设备之间的通信,作为RS 232通信接口的一个重要的部分,目前大部分的处理器都集成了UART。

l UART的数据格式

UART的数据传输格式如图1所示。

由于数字图像亚像素在计算机中是用8位二进制表示,因此UART传输的有效数据位为8位。传输线在空闲时为高电平,因此有效数据流的开始位设为0。接着传输8位有效数据位,先从最低位开始传送。奇偶检验位可以设置为奇检验、偶校验或者不设置校验位,由于本系统使用的传输速率不高,为了加快开发进程,减少电路面积,因此没有设计奇偶检验模块,数据流中不设奇偶检验位。最后停止位为高电平。

2 UART的基本结构

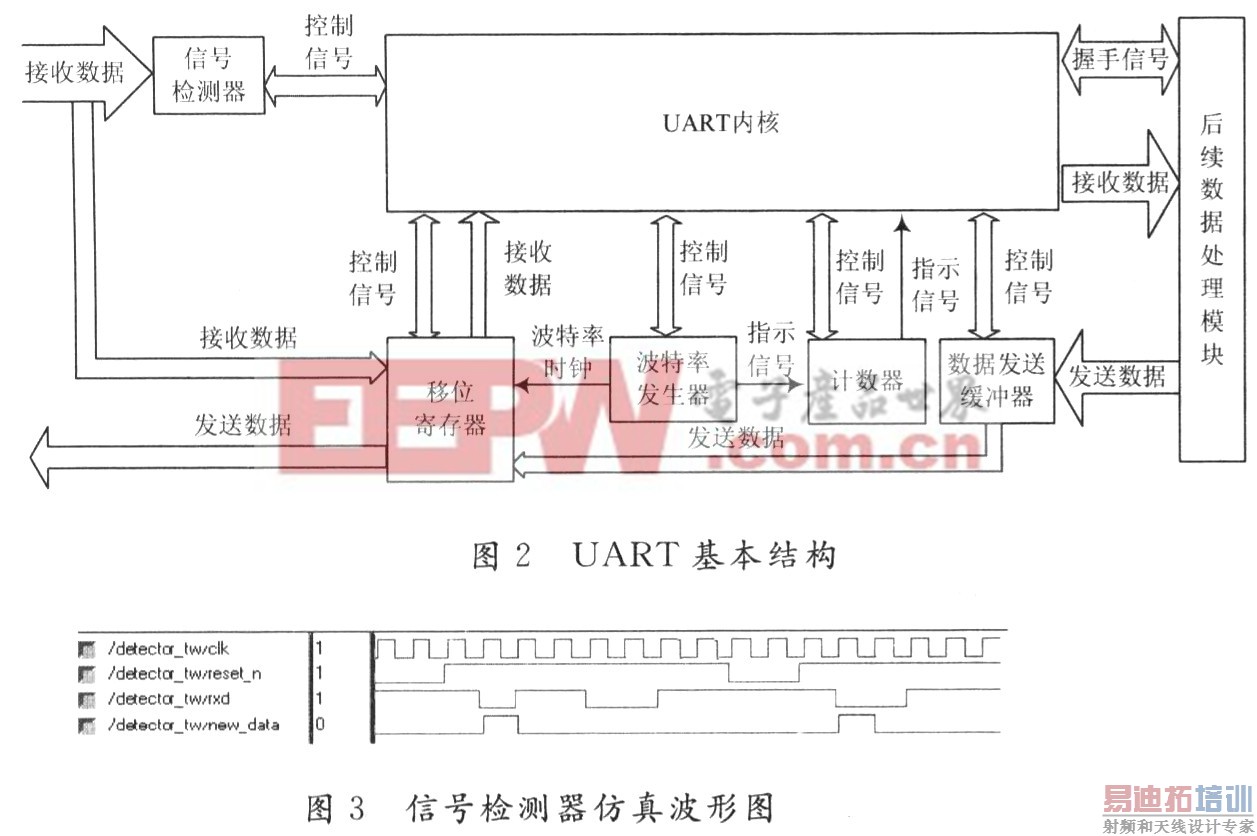

设计的UART主要由UART内核、信号检测器、移位寄存器、波特率发生器和计数器组成,如图2所示。UART各个功能模块的功能如下文所述。

2.1 信号检测器模块[p]

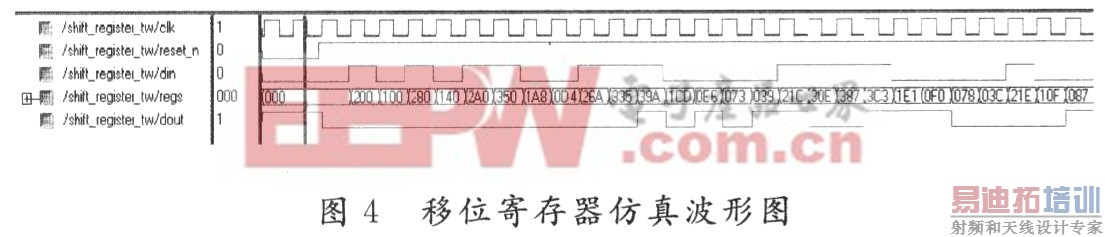

信号检测器用于对RS 232的输入信号进行实时监测,一旦发现新的数据则立即通知UART内核。信号检测器的仿真波形如图3所示。

其中,RxD第一次为低时,new_data信号阐述输出,之后RxD又变低,但由于信号检测器处于锁定状态,所以 new_data信号并没有输出;最后,reset_n信号将信号检测器复位,RxD再次变低时,new_data又有输出。可见信号检测器的实现完全正确,其功能完全符合设计要求。

2.2 移位寄存器模块

移位寄存器模块的作用是存储输入或者输出数据。当UART接收RS 232输入时,移位寄存器在波特率模式下采集RS 232输入信号,且保存结果;当进行RS 232输出时,UART内核首先将数据加载到移位寄存器内,再使移位寄存器在波特率模式下将数据输出到RS 232输出端口上。移位寄存器的仿真波形图如图4所示。

如图4所示,移位寄存器在复位后的每个时钟的上升沿工作。由于数据发送时是先发送有效数据的最低位,因此移位寄存器是将接收的数据由高位向低位移动,dout输出移位寄存器的最低位。图中的regs数据用16进制表示。

2.3 波特率发生器模块

波特率发生器的功能是产生和RS 232通信所采用的波特率同步的时钟,这样才能方便地按照RS 232串行通信的时序要求进行数据接收或者发送。比如,波特率为9 600 b/s,即每秒传输9 600 b数据,则同步的波特率时钟频率为9 600 Hz,周期为1/9 600=O.104 17。设计波特率时钟的基本思路就是设计一个计数器,该计数器工作在速度很高的系统时钟下,当计数器计数到某数值时将输出置高,再计数到一定的数值后再将输出置低,如此反复便能够得到所需的波特率时钟。该系统所用的FPGA系统时钟为50 MHz,RS 232通信的波特率为9 600 b/s,则波特率时钟的每个周期相当于![]() 5 208个系统时钟周期。假如要得到占空比为50%的波特率时钟,只要使得计数器在计数到1 604时将输出置高,之后在计数到5 208时将输出置低并且重新计数,就能实现和9 600波特率同步的时钟。

5 208个系统时钟周期。假如要得到占空比为50%的波特率时钟,只要使得计数器在计数到1 604时将输出置高,之后在计数到5 208时将输出置低并且重新计数,就能实现和9 600波特率同步的时钟。

为了便于仿真,使计数器计到2时将输出置高,之后计到4时将输出置地并且重新计数。波特率发生器的仿真波形图如图5所示。

观察波形可以看到波特率发生器每经过4个时钟周期输出1个完整的波特率时钟周期,占空比为1/2,并且在每次输出波特率时钟周期之后输出1 个系统时钟脉宽的提示信号indicator,UART通过此信号来了解波特率发生器已输出的波特率时钟周期个数。由波形图可见波特率发生器的工作完全满足设计的要求。

2.4 计数器模块

计数器模块的功能是可控的,在输入时钟的驱动下进行计数,当达到计数上阈时给UART内核一个提示信号。在不同的工作状态下,计数器模块的输入时钟是不同的。UART在数据发送之前需要进行数据加载(即将串行序列保存在移位寄存器内),在此工程中计数器模块的输入时钟为系统时钟,因为此时移位寄存器也工作在系统时钟下。除了数据加载,另外2个需要计数器模块的过程是数据接收和数据发送。

由于这两个过程中移位寄存器工作在波特率时钟下,所以计数器模块的时钟就是与波特率时钟同步的波特率发生器提示信号iladicator,这样每输出1个完整的波特率时钟周期计数器就能增加1。

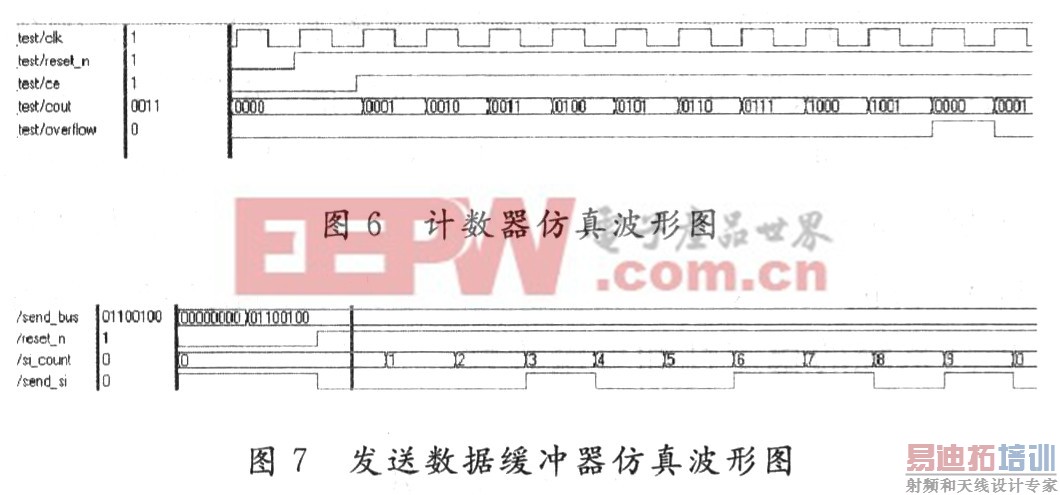

计数器的仿真波形图如图6所示。

计数器在复位后并且ce有效时开始计数,并且在第10个时钟周期输出提示信号overflow。

2.5 发送数据缓冲器模块[p]

发送数据缓冲器模块的功能是将要发送的并行数据转换成串行数据,并且在输出的串行数据流中加入起始位和停止位。缓冲器首先将要发送的8位数据寄存,并在最低位后添加起始位‘O’,在最高位前添加停止位‘1’,组成10位要发送的数据。然后根据 UART内核模块的计数值将相应的数据送入移位寄存器输入端。

UART内核模块输出的计数值是从0依次计到9,即先将要发送数据的最低位送入移位寄存器。发送数据缓冲器的仿真波形图如图7所示。

由波形图可知,发送数据缓冲器在复位后,在输入的计数值si_count为0时,send_si输出起始位‘O’。在输入的计数值 si_count为1~8时,send_si分别输出send_bus上相应的数据位。在输入的计数值sl_count为9时,send_si输出停止位 ‘1’。

2.6 UART内核模块

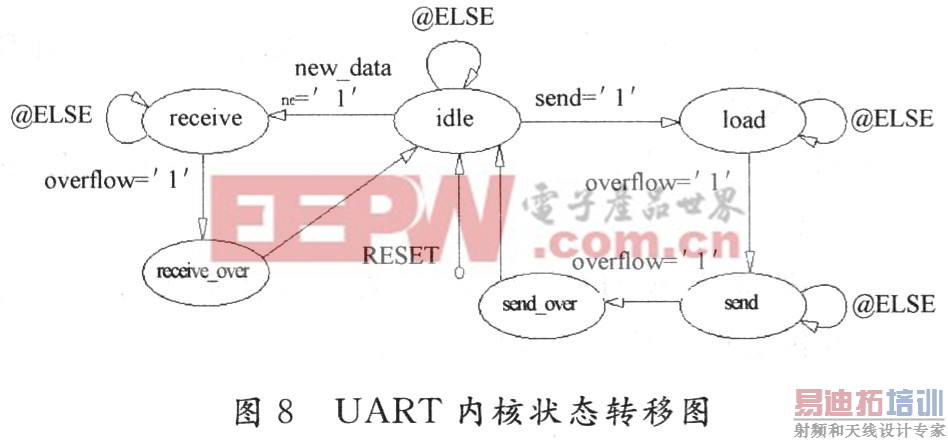

UART内核模块是整个设计的核心。在数据接收时,UART内核模块负责控制波特率发生器和移位寄存器,使得移位寄存器在波特率时钟的驱动下同步地接收并且保存RS 232接收端口上的数据。在数据发送时,UART内核模块首先根据待发送数据产生完整的发送数据序列(包括起始位、数据位和停止位),之后控制移位寄存器将序列加载到移位寄存器的内部寄存器里,最后再控制波特率发生器驱动移位寄存器将数据串行输出。UART内核模块的主要功能是控制数据接收、数据加载和数据发送的过程,这可以用状态机来实现,其状态图如图8所示。

(1)数据加载过程。数据的接收过程可以定义3个状态:空闲“idle”状态、接收“receive”和接收完成 “receive_over”。UART内核模块在复位后进入空闲状态。如果信号检测器检测到数据传输,即new_data一‘1’,UART内核检测到此信号就会进入接收状态。在UART进入由空闲状态转为接收状态过程中,需要进行一系列的接收预备操作,包括将子模块复位、选择移位寄存器串行输人数据以及选择移位寄存器的输入时钟等。进入接收状态后,波特率发生器开始工作,其输出波特率时钟驱动移位寄存器同步的存储RS 232接收端口上的数据,并且其提示信号“indicator”驱动计数器进行计数。当所有数据接收完成,计数器也达到了其计数的上阈,此时 overflow=‘1’,通知UART内核进入接收状态。UART内核进入接收完成状态的同时,会检查奇偶校验的结果,同时使得子模块使能信号无效,以停止各个子模块。

UART内核的接收完成状态仅保持1个时钟周期,设置这个状态的作用是借用一个时钟周期复位信号检测器,准备接收下次数据传输。

(2)数据加载和发送过程。数据加载和发送的过程都是为发送数据而设定的,所以将它们放在一起进行介绍,可以用4个状态来实现上述的过程,即空闲、加载、发送和发送完成。其中的空闲状态是UART内核复位后的空闲状态,与上面介绍的数据接收过程的空闲状态一致。数据加载过程在数据发送过程之前进行。UART内核复位后进入空闲状态,当探测到发送控制信号有效时,即send=‘1’,便会进入加载状态开始数据加载。在进入加载状态的同时,UART内核会将移位寄存器、计数器复位,并且通过选择信号使得移位寄存器的输入为发送数据缓冲器模块产生的串行数据序列,使得移位寄存器和计数器的工作时钟为系统时钟。进入加载状态后,在UART内核控制下,发送数据缓冲器模块会将完整的待发送序列加载到移位寄存器的数据输入端,发送的序列是和系统时钟同步的,移位寄存器在系统时钟的驱动下不断读人输入端数据并保存在内部寄存器内。在移位寄存器加载数据的同时,计数器也在时钟的驱动下进行计数,由于都是工作在系统时钟下,所以当所有数据被加载时,计数器也达到了计数的上阈(即串行数据的总量),此时overflow=‘1’,通知UART内核进入发送状态。UART内核进入发送状态的同时会改变几个选择信号,比如将移位寄存器的时钟设为波特率时钟,将计数器时钟设为波特率的提示信号,最重要的是将输出信号送到RS 232的发送端口TxD上。发送的过程和接收类似,移位寄存器在波特率时钟的驱动下内部寄存器的数据串行的发送出去,同时计数器在波特率发生器的提示信号驱动下进行计数。UART内核在计数器到达计数上阈后便进入发送完成模式,并且输出发送完成信号。

3 UART顶层模块的仿真测试

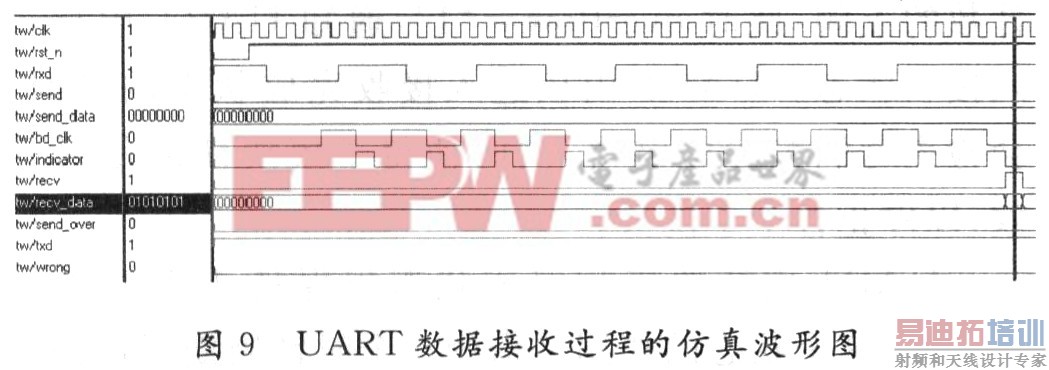

将上述各个模块的VHDL代码生成原理图符号,并在原理图编辑工具中将各个模块连接起组成1个完整的UART模块。为了验证 UART模块的正确性,对UART的发送过程和接收过程分别进行了波形仿真。为便于观察波形,波特率产生器设置为4个系统时钟产生一个完整的波特率时钟。图9是UART模块接收过程的仿真波形图。

由仿真波形图可以看出,接收端RxD上的数据序列为0101010101,起始位‘O’后为数据位“10101010”,最后一位为停止位 ‘1’。在10个波特率时钟之后,UART发出1个接收完成信号recv一‘1’,并在数据输出端“new_data”将接收的数据输出给后续数据处理模块。由于发送数据时首先发送数据的最低位,因此接收的数据应为“01010101”,将光条放置数据输出端“new_data”的数据输出波形上,可以从数据栏看到此时数据输出端new_data=“01010101”,UART数据接收功能完全正确。

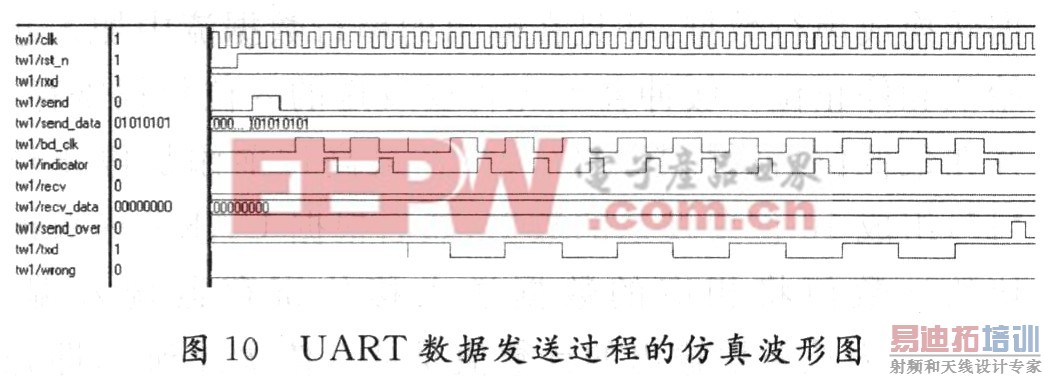

图10为UART发送过程仿真波形。由图可以看出,send=‘1’后待发送数据为“01010101”,将待发送数据加上起始位和停止位,并从最低位开始发送,则发送端txd上的数据序列为“0101010101”,发送停止位后,发送结束信号send_over=‘1’。图10 证明UART数据发送功能完全正确。

4 结 语

介绍了UART在可编程逻辑器件FPGA上的实现,并通过实际电路验证了设计的功能,使用FPGA不仅可以方便地用串口协议与PC 机进行串行通信,而且扩展了板级系统的接口功能。应用在可编程器件FP―GA内部,可以很大程度地减少电路板的使用面积,并提高系统的稳定性和可编程性。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...