- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

1553B总线远程端点数据链路层协议的FPGA实现

0 引 言

用于车辆、舰船、飞机等机动平台上的电子设备越来越多,并且越来越复杂。将电子设备加以有效的综合,使之达到资源和功能共享已成为必然趋势。电子综合的支撑技术是联网技术,而机动平台上的联网技术不同于一般的局域网技术,它特别强调网络的可靠性和实时性。1553B总线是在20世纪70年代末为适应飞机的发展,由美国提出的飞机内部的电子系统联网标准;其后由于它的高可靠性和灵活性而在其他机动平台上得到了广泛应用。国内上世纪80年代中期已开始接触这类技术,目前它的研究与应用范围正在迅速扩大。

1553B总线标准由美国军方制定。支持该标准的协议芯片有DDC公司的BU一6517X,BU一615XX系列;HOLT公司的HI一61XX系列;UTMC公司的BCRTM等。这些芯片都集成了BC,RT,BM的功能,但是这些芯片都由美国公司生产,价格非常昂贵。为了能低成本地使用这种可靠性非常好的数据总线,采用FPGA设计并实现远程端点的数据链路层协议,通过外接一个总线收发器完成1553B远程端点协议芯片功能。

在电子设计领域,可编程逻辑器件的广泛应用为数字系统的设计带来极大的灵活性,1片FPGA芯片可代替上百个IC电路。Altera公司开发的Cyclone系列FPGA芯片价格便宜,功能强大,而且配套的开发软件QuartusⅡ更是集成了时序仿真、编译、综合、优化等功能,这为实现1553B总线远程节点通信协议提供了有利条件。文中所实现的1553B总线远程端点数据链路层协议采用VerilogHDL语言编写;采用ModelSim仿真;采用QuartusⅡ编译、综合、优化,并在A1tera的EPlC6系列FPGA上实现。

1 1553B总线及其接口功能

1553B的全称是:飞机内部时分制指令/响应式多路传输数据总线。它对物理层,如:传输介质、屏蔽条件、耦合方式、阻抗匹配以及输入输入兼容性等都做了严格规范。1553B总线是以串行数据脉冲的形式进行传输的,其数据用双相曼彻斯特码的形式来表示,其传输速率为1 Mb/s。1553B数据总线上连接有3种类型的节点:

(1)总线控制器(BC):控制总线上的数据传输;

(2)远程终端(RT):响应BC命令,执行相关操作;

(3)总线监视器(BM):有选择地接收数据总线上的信息并保存。

飞机上的每个子系统可以通过1553B总线连接到任何一个系统中并与其通信。

在总线上传输字有3种类型:命令字、状态字和数据字。每种字的字长为20位,有效信息位为16位,每个字的前三位为同步字头,最后一位为奇偶校验位。有效信息(16位)及奇偶校验位在总线上以曼彻斯特码的形式进行编码,每位占的时间为1μs。同步字头占3位,或先正后负(命令字、状态字)或先负后正(数据字),正、负电平各占1.5μs,即占同步头位场的50%。

由于系统类型的不同,可辨别出命令字和状态字,命令字由总线控制器发出,而状态字由远程终端RT发出。

作为1553B总线的远程端点,应完成以下功能:

(1)将总线上的串行信息流转换成微控制器可以处理的并行信息或者与之相反;

(2)接收或者发送信息时,能够识别或生成标准的1553B信息字;

(3)完成与微控制器之间的信息交换,包括1553B信息地址的分配、命令字的译码或返回状态字、发送数据字等。

1553B远程端点数据链路层协议需要完成上述的1553B远程端点的大部分功能,包括同步头添加与检测,曼彻斯特码编解码,命令字译码与接收数据字,状态字反馈与收发数据字,数据缓冲以及与微控制器之间的接口等。整个数据链路层协议内部采用寄存器控制的方式进行操作,上层微控制器通过读写实现程序的寄存器,以完成对协议的控制,而内部操作也是根据相关寄存器的状态来进行的,因此设计时,首先定义相关寄存器,根据数据线的宽度,所有寄存器都定义为16位。

(1)控制寄存器:它完成内部时钟、总线端口选择、节点状态设定、状态字保留位、节点ID以及全局复位等状态的设置和操作。

(2)错误寄存器(ER):当通信协议中出现了奇偶校验错误,数据不连续错误,接收数据个数错误,接收FIFO错误,发送FIFO错误时就会置位其相关位,上层微控制器通过读取ER就知道错误的类型。

(3)状态寄存器(SR):SR中反映了当前数据链路层协议的状态,包括接收数据状态、接收FIFO长度、发送FIFO长度、接收错误状态、中断信号状态nINT和nINTD。

(4)接收命令字寄存器(RCR):RCR用于保存当前接收到的命令字。

(5)发送矢量字寄存器(SVWR):该寄存器用于存放总线控制器要求的矢量字,这个矢量字由微控制器写入。

(6)接收同步字寄存器(SYNDR):用于存放接收到的带数据字同步命令中的数据字。[p]

(7)自测结果寄存器(STRR):STRR用于存放上次自测的结果。为了方便地址分配,设计中把发送和接收FIFO都作为一个16位寄存器来对待。

2 1553B远程端点数据链路层协议的FPGA实现的总体设计

1553B远程端点数据链路层协议的FPGA实现一共分为4个模块:序列解析模块、命令解析模块、发送模块和上层交互模块。整个协议实现采用时序驱动的方式进行,时钟频率为8 MHz,下面就按照数据进入的顺序介绍整个协议的FPGA实现过程。

2.1 序列解析模块

这个模块接收从收发器接收的信号序列,先后进行同步头检测,曼码解码,奇偶校验,ID检测等步骤,最后给命令解析模块一个只包含命令信息的16位数据,以及其字特性。其实现流程如图1所示。

序列解析模块首先对进入的总线序列进行同步头检测,如果有效,则进行曼彻斯特码解码。曼彻斯特码解码是在同步头检测有效时同步开始的,它在同步头检测有效后每隔1 000μs对序列采样一次,并把采样值作为解码值,同时判断在采样时序列是否发生了跳变,如果发生,则说明序列满足曼彻斯特码编码,否则认定序列存在编码错误,停止解码并置位错误寄存器,而第一次采样是在同步头检测有效后250ns。解码完成后进行奇偶校验,接收模块对有效序列进行奇偶校验,如果奇偶校验错误,则丢弃这个序列,同时置位消息差错位;如果奇偶校验正确,则进入ID检测部分。奇偶校验在VerilogHDL中通过位异或就可以实现。

当奇偶校验正确以后,接收模块就根据从同步头检测得到的字类型进行不同操作。对于数据字,接收模块收到序列后就检测等待数据字寄存器的值,如果不为零,则把这个数据放入到接收缓冲器中,如果等待数据字寄存器的值为1,则首先把寄存器清零,然后把中断请求信号置位,最后把状态寄存器的值放入发送缓冲器中,并通知发送模块发送以及复位等待数据字寄存器,否则把等一待数据字寄存器的值减1,等待下一个字的到来。如果等待数据字寄存器值为零,则认为传输错误,丢弃这个数据字。对于命令字,接收模块进行ID验证,检查所收到的命令是否是总线控制器发给本节点的。它提取所收到的16位有效信息序列中的高5位,与本节点的ID比较,如果不相同,则丢弃这个序列,等待下一个序列的到来;如果相同,则表示这个序列是总线控制器发给本节点的命令,保存命令,启动命令解析模块。

2.2 命令解析模块

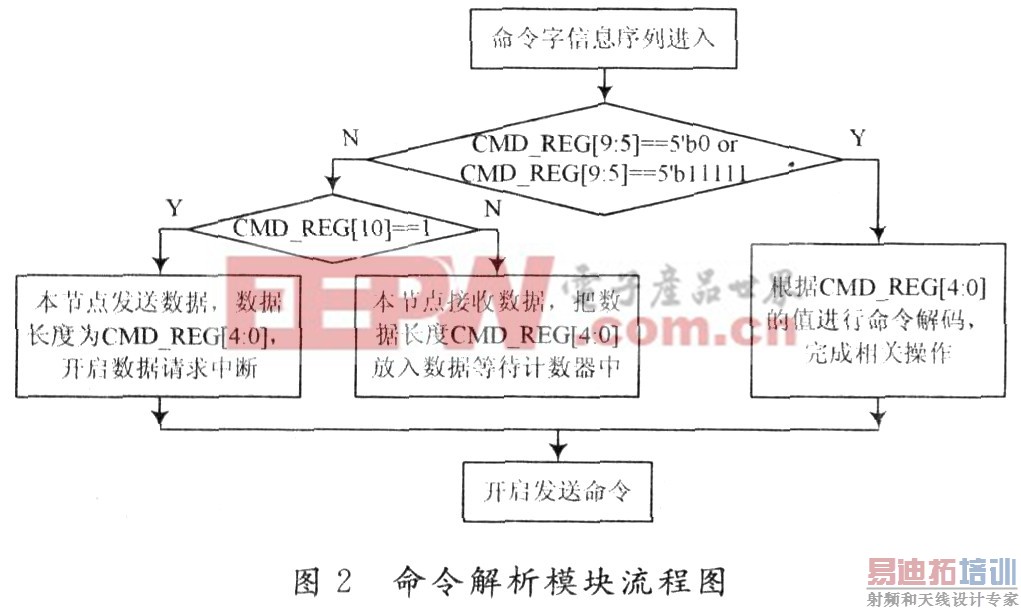

命令解析模块完成对收到的命令字进行解析,对收到的数据进行存储的工作。命令解析模块是整个协议的核心,它负责把总线控制器传给本节点的命令翻译成本节点的操作,并执行相关动作。其工作流程如图2所示。

假设命令字存放在寄存器CMD―REG[15:0]中,则命令解析模块首先检测CMD REG[9:5],如果CMD REG[9:5]不为全1或者全0,就表示总线控制器给节点的是数据传输命令;命令解析模块则继续检测CMD REG[10]位,如果为1,则表示总线控制器要求本节点发送数据,同时用CMD REG[4:0]指定了需要发送的数据长度;命令解析模块在收到这个命令后就把相关的数据和状态寄存器的值装入发送缓冲器中,并通知发送模块进行发送。如果CMD REG[10]位为O,则表示总线控制器要求本节点接收数据,同时也用CMD REG[4:0]指定了接收数据的长度,而用CMD REG[9:5]指定了数据接收子节点的ID,命令解析模块在收到这个命令以后就把CMD REG[4:O]装入等待数据字寄存器中,等待后继数据字的到来。如果CMD REG[9:5]为全1或者全O,则表示总线控制器传输的控制命令字,并通过CMD REG[4:0]指定了相应的命令方式代码。对于命令方式代码,命令解析模块根据1553B总线标准对不同方式代码进行相关的寄存器置位操作。

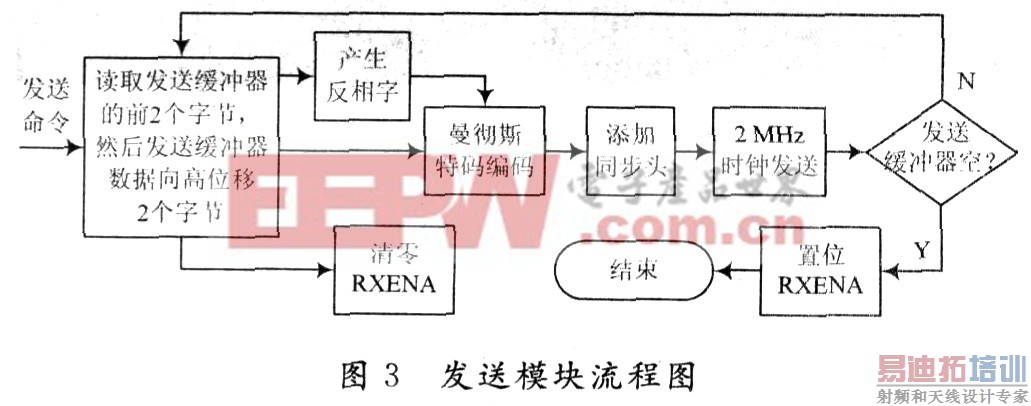

2.3 发送模块[p]

命令解析完成后都需要进行状态反馈或者数据发送,而完成这个功能的是发送模块,发送模块负责把命令解析模块和接收模块装载到发送缓冲器中的数据发送到总线上去,如图3所示,它包括读取数据,产生反相字,曼彻斯特码编码,添加同步头,2 MHz时钟数据发送等几个部分,同时由于发送缓冲器中数据有可能多于2个字节,因此还可能需要循环进行这个操作。下面就根据发送的具体流程设计每个部分。首先是发送缓冲器部分,当接收到发送命令后,发送模块就第一次读取发送缓冲器的前两个字节,因为这两个字节肯定是状态字,然后把这两个字节贴上状态字标签,继续传给后继单元,待完成以后就把接收发送缓冲器的发送数据长度寄存器减1,并把发送缓冲器中的数据向前移动2个字节。如果发送数据长度寄存器不为零,则继续等待下一次的发送。

2.4 上层交互模块

最后一个模块是上层交互模块,这个模块负责与上层微控制器进行信息交互,它负责把微控制器写入的数据放入相应的寄存器中,或者按上层微控制器的命令回传相关的数据。上层交互模块主要包括边沿信号与电平信号转换、地址解码和读写寄存器。因为协议实现模块中采用的是边沿信号触发,而上层微控制器给FPGA的信号是电平信号,要顺利地完成通信,就需要进行转换,这里通过锁存器和计数器来完成。地址解码就是把收到的地址解码成相应寄存器的地址,然后写入收到的数据或者把寄存器中的数据读出放入到数据总线上。

3 仿真及FPGA实现

为了确保设计的可行性,必须对设计进行时序仿真。整个协议VerilogHDL实现程序在Altera公司的FPGA开发软件QuartusⅡ中编写、编译、综合。整个程序的仿真在Modelsim 6.0中进行,其仿真过程如下:

(1)接收数据。总线控制器发送给实现程序两个数据:0x1234和Ox5678,上层微控制器在实现程序接收数据后通过上层交互模块把数据读出,其中第一个数据包含了接收数据长度,通过图4可以看出整个过程顺利进行,完成了预定目标。

(2)发送数据。总线控制器间隔地发送给实现程序两个发送数据的命令,让实现程序反馈相关的数据,这些数据是通过上层交互模块提前写入到实现程序中的,其仿真过程如图5。通过图5也可以看出在实现程序接收到命令到发送出数据的延时时间大约为4μs,完全符合1553B总线对远程端点反馈信号延时的规定。

(3)一般命令。总线控制器发送给实现程序一般的方式代码命令,代码分别为:000ll,10010,01111和00001,其仿真过程如图6所示。可见,实现程序正确地反馈了相关信息,符合设计要求。 [p]

[p]

该设计在仿真正确以后,通过QuartusⅡ优化、综合,最后在Altera公司的Cyclone系列FPGA上进行了具体的实现,并与Freescale公司的16位单片机MC9S12XDP512一起组成了1553B远程端点,通过1553B收发器联入到了1553B总线系统中,成功地完成了远程端点的协议。这说明采用FPGA实现程序设计的1553B远程端点通信协议完全正确,达到了预期的目的。

4 总结及设计通用性

用于1553B远程端点数据链路层协议的FPGA实现程序采用自顶向下和自下向上相结合的方式进行设计,用Veri1ogHDL语言编写;用Modelsim和QuartusⅡ进行仿真和综合。在最后,针对特定器件做了再一次的优化,缩短了设计周期,提高了系统性能,并且大大提高了芯片资源的利用率。

该设计具有较高的通用性,与外部的接口采用标准的通信接口方式进行。它对于上层微控制器来说就是一个内存单元,上层微控制器通过对相关地址的读写即可完成对整个通信协议的控制,应用非常简便,还可以封装成模块,嵌入到NiosⅡ等处理器中,成为其内部的一个控制器。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...