- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的多功能信号源生成系统设计与实现

摘 要:为了满足科研与实验需要,提出并实现了一种以FPGA和高速D/A为核心,其结构简单,控制灵活,信号质量高的多功能信号源生成系统。该信号源生成系统能够实时产生中心频率在30~130 MHz的各种雷达、通信、导航和白噪声等信号,且产生的各种信号频率、幅度、相位和其他参数均可控。信号源作为基带信号单元配以混频模块,可实现在任意频段的信号。另外,该信号源还可以作为一个通用平台,通过FPGA内部程序的更新来实现其他复杂信号。

关键词:FPGA;信号源;硬件设计;AD9736

产品级的信号源往往满足不了科研和实验的需要,尤其在复杂电磁环境的研究和实验中,需要的信号样式多种多样,而且根据场景的不同,需要信号样式、个数都发生了改变。

现场可编程逻辑阵列器件(FPGA)继承了ASIC中大规模、高集成度、高可靠性的优点,克服了普通ASIC设计周期长,投资大,灵活性差的缺点,逐步成为复杂数字硬件电路设计的理想首选。为了能满足科研与实验的需要,产生一系列需要的信号,设计了一种以FPGA和高速D/A为核心.能产生中心频率在30~130 MHz的、各种参数均可调的雷达、通信、导航和噪声信号的多功能信号源生成系统。

1 系统硬件结构

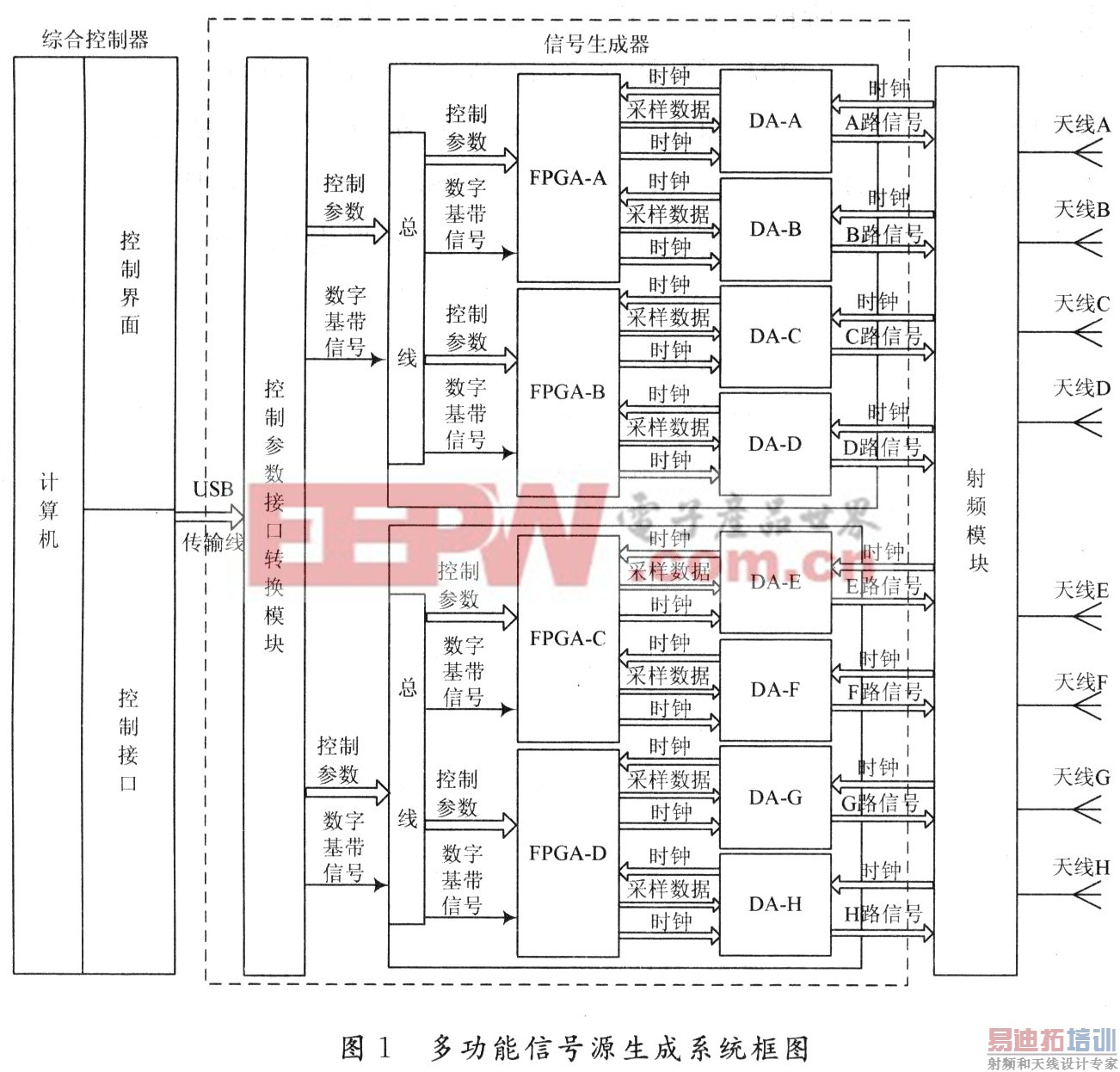

多功能信号源生成系统在综合控制器的控制下产生一个或多个中心频率在30~130 MHz的雷达、通信、导航、噪声等信号,输出电平一60~o dBm.步进值为0.06 dB。系统主要由综合控制器、信号生成器、射频模块和天线4个部分构成,如图1所示。综合控制器实现对系统的整体控制,包括信号路数及各路信号参数。信号生成器主要包括控制参数接口转换模块和信号生成模块两个部分。射频模块主要完成两项功能,即650 MHz时钟的生成和对输入的中频信号变频,最后经天线输出信号。

2 综合控制器

综合控制器为一台工控计算机,主要完成控制参数的输入和数字基带信号生成。控制人员通过综合控制器控制界面将控制参数输入,这些控制参数经过计算机uSB接口输入到信号生成器,实现对信号生成器的控制。数字基带信号是一定速率的二进制码流,在该系统中综合控制器完成将BMP图片转换成一定速率的二进制数据,并通过USB接口输人到信号生成器中,作为系统的数字基带信号。综合控制器在工作时,负责向信号生成器注入控制参数,如信号路数和各路信号参数(信号样式、工作频率、功率输出、调制指数、延迟时间、跳频速率、脉宽、脉冲周期等),当控制参数输入完毕后,综合控制器开始利用USB接口传输由BMP图片转换的二进制数据。系统在工作过程中可实时更改控制参数,并根据指令进行刷新,此时数字基带信号传输将暂停,等待更新完毕后继续输出。

3 信号生成器

信号生成器由两部分构成,即控制参数接口转换模块和信号生成模块。控制参数接口转换模块完成将综合控制器通过USB传输线传输的控制参数和数字基带信号转换为总线数据送入总线中,由信号生成模块产生特定控制参数的信号。[p]

3.1 控制参数接口转换模块

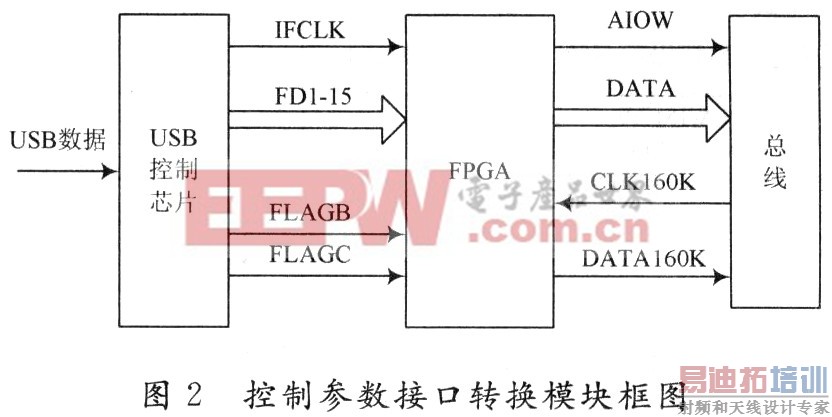

控制参数接口转换模块完成从USB接口中收到的数据接收,并将接收数据转换为总线数据送入背板总线。控制参数接口转换模块主要包括两个部分:USB控制芯片和1片FPGA,如图2所示。在这个模块内完成数据包的获取和拆分两个操作。数据包的获取就是USB控制芯片将USB传输线中的1位数据转换为16位的FD信号,送到FPGA中。FPGA再将接收到的数据按照数据包拆分协议分成16位控制参数信号DATA与160 kHz的数字基带信号DATAl60K送到背板总线,同时通过总线进行传输的还有两个时钟信号AIOW和CLKl60K。其中AIOW是与控制参数信号DATA相匹配的时钟,是由FPGA送入总线中的,而CLKl60K是与数字基带信号DATAl60K相匹配的时钟,是由信号生成器通过总线送入FPGA中的。数据包的拆分主要由1片Spartan3 FPGA(XC3S200)来实现。

3.2 信号生成模块

信号生成模块采取FPGA和高速D/A相结合的方法,在FPGA内部产生高速采样数据。采样数据送人高速D/A中还原出信号。在该系统中,FPGA芯片选用Xilinx公司Virtex-4系列的XC4VLXl00,而高速D/A选用AD公司的AD9736。如图1所示,信号生成模块包括2块信号生成电路板,每块电路板上有2块FPGA和4块高速D/A,每块FPGA与2个D/A相连,即1个FPGA内部需要同时产生2路信号采样数据,整个系统能产生8路信号。

FPGA的工作时钟是射频模块生成的时钟在高速D/A内完成二分频后送给FPGA的。由于每块FPGA与2个D/A相连,因此它也有2个时钟输入。为了保持时钟与数据的同源特性,在FPGA内部电路设计中采取了并行设计的方法,即送给高速D/A的高速采样数据与其匹配的时钟完全是由其送入的时钟来产生的,而与另一个D/A送入的时钟完全无关,保持了各路信号之间的独立性。同时,射频模块可以产生相参和非相参的时钟,从而使得系统能产生相参和非相参信号。另外,送入D/A的时钟也可由外部送入,大大增加了系统的灵活性。

FPGA内部采取了模块化设计方法,包括参数分配模块、各种信号采样数据生成模块和信号求各种信号采样数据生成模块和信号求和模块,其设计框图如图3所示。参数分配模块主要将总线接收到的各路信号中控制参数信号DATA分配到各信号采样数据生成模块中,其内部控制示意图如图4所示。参数分配模块在时钟AIOW的上升沿时刻,按照控制参数信号DATA的高位情况,识别DATA低15位为地址还是数据,如果为地址则送往地址锁存器锁存;如果为数据则送往地址译码器,由地址译码器根据译码协议判定数据为特定信号采样数据生成模块的特定控制参数。信号采样数据生成模块则根据所分配的参数生成所需信号采样数据送往求和模块。为了减少信号经过求和模块带来信号能量的损失,设计中不是采用传统截取高位输出的方式,而是采取了截取低位输出的方式,这种方式保证了求和器在没有溢出的情况下,能维持系统指定参数的信号输出,而不损失信号能量。为了防止求和器溢出,产生失真信号,在综合控制器中做相应处理,使得控制人员输入的控制参数在合适的范围之内。

[p]

[p]

信号采样数据生成模块可将生成在这种模式下的一个或多个信号组合,而且可以根据需要.通过输入控制参数,实时改变组合的模式。图3中只表示了一种模块的组合关系,如果在这种组合下还不能满足实验和科研需要,系统可以通过重新进行软件编程,下载到FPGA中,从而得到所需信号采样。

4 AD9736简介

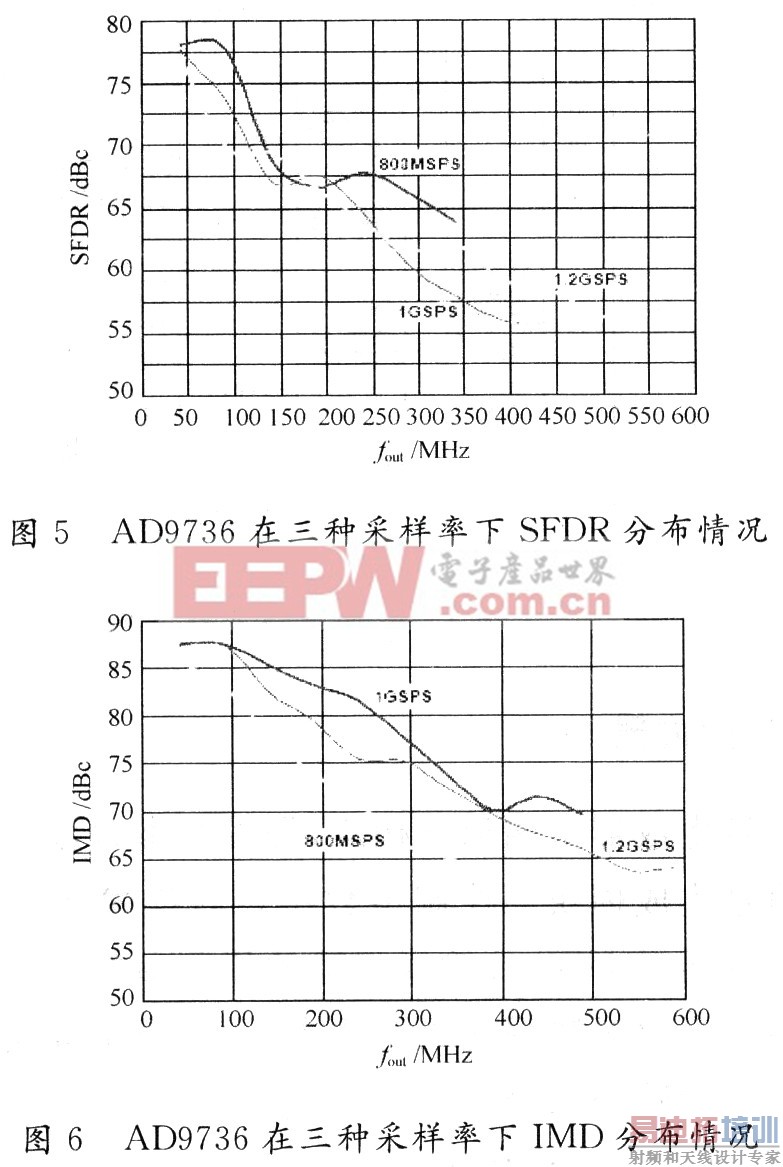

AD9736是由AD公司.生产的一种14 b高速DAC,其采样时钟速率突破了1 GSPS,达到1.2 GSPS,且功耗极低。AD9736的输出电流在10~30 mA范围内可编程,并且很容易配置单端或差分输出电路结构。AD9736采用LVDS数据接口,可以有效保证高速数据的传输。AD9736内部支持两倍插值,且内嵌了一个55阶的对称FIR插值滤波器,该滤波器通带内平整度为O.001 dB,阻带衰减达到90 dB,过渡带为20%~30%,从而大大降低采样数据速度。文献[2]列出了AD9736在800 MSPS,1 GSPS和1.2 GSPS采样率下无杂散动态范围(SFDR)和互调失真(IMD)情况,如图5,图6所示。该器件在1.2 GSPS采样速率下,255 MHz输出频率时互调失真(IMD)为74 dBc,并且在600 MHz输出频率时IMD优于60 dBc,sFDR在300 MHz输出频率时为62 dBc。

5 系统性能

该信号生成系统能够实时产生单个或多个中心频率在30~130 MHz的各种信号,如单音、调幅、调相、调频、ASK、FSK、BPSK、QPSK、跳频、直扩、白噪声等,还可以模拟各种雷达发射脉冲和回波信号。另外,还可以通过ISE编程和重新下载程序到FPGA中实现更复杂的信号。

该系统产生的信号在频率、幅度和其他各种参数均实现可调,频率分辨率达到0.35 Hz,输出电平为-60~O dBm,步进值为0.06 dB时,SFDR优于60 dB。由于该系统能同时发射多路信号,并且有多个天线,因而可用于模拟从不同方向上发射多路信号复杂的模拟电磁环境。同样,该系统还可以作为干扰源和信号源用于各种干扰与抗干扰的试验研究。图7和图8分别为系统产生的FSK信号波形和频谱图;图9和图10分别为系统模拟FSK信号经过多路径传输的波形和频谱图。

6 结 语

利用FPGA和高速D/A相结合实现的信号源,结构简单,控制灵活,性能优越,还可以根据需要在这个平台上,重新下载程序到FPGA中,更改其内部电路,而不用另外制板,这样既节省时间,也减少开销,还有利于信号源的改进。另外,系统还可以作为基带信号单元,结合混频电路在任意要求的频段上实现多种样式的信号。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...