- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的脉冲压缩仿真与实现

1 引言

随着现代武器与航天技术的发展,要求雷达应具有高精度、远距离、高分辨力等性能。简单矩形脉冲雷达存在雷达探测能力与距离分辨力之间的矛盾。为解决这一矛盾,大多数现代雷达采用脉冲压缩技术,调制信号频率或相位,从而产生大时宽带宽信号,接收端通过具有匹配滤波器的接收机接收,产生窄时间脉冲,提高距离分辨率。以数字方式实现的脉冲压缩具有可靠性高、灵活性好、可编程、便于应用。因此,这里介绍一种分布式算法实现时域脉冲压缩,它是一种基于查找表的计算方法,通过将各输入数据每一对应位产生的部分积预先相加形成相应部分积,然后再对各部分积累加形成最终结果,从而实现乘加功能。与传统算法(所有乘积产生后,再相加完成乘加运算)相比,分布式算法可极大减少硬件电路规模,易于实现流水线处理,提高电路执行速度。

2 脉冲压缩

2.1 脉冲压缩处理过程

脉冲压缩处理有时域和频域两种方式。其中.时域处理是由数字有限冲击响应(FIR)实现的过程,即信号与系数的卷积;而频域处理则是先用FFT计算出数字回波信号的频谱S(ω),再将其与匹配滤波器的频响H(ω)相乘,最后进行快速傅里叶反变换(IFFT),得到脉压结果。一般而言,对于大时宽带宽信号,采用频域处理较好;对于小时宽带宽信号,采用时域处理较好。脉冲压缩信号实现方法有:线性调频信号、非线性调频信号和相位编码信号。线性调频信号是通过非线性相位调制或线性频率调制(LFM)来获得大时宽带宽积。与其他脉冲压缩信号相比,它具有匹配滤波器对回波信号的多普勒频移不敏感的优点。这里采用的LFM信号是由一个匹配滤波器来处理,并具有不同多普勒频移的信号。

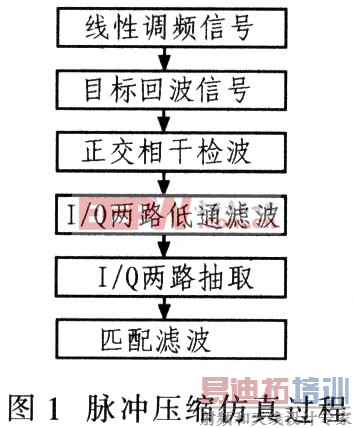

IFM数字脉冲压缩仿真流程包括线性调频(LFM)信号产生、回波信号的模拟、正交相干检波、I/O两路信号低通滤波及抽取、视频信号(零中频)匹配滤波,如图1所示。作为关键部分的匹配滤波器,它是一种线性相位的FIR滤波器,其滤波器系数为发射信号的复共轭,h(n)=x*(N-n),而为了降低旁瓣,一般给系数加上相应权值。

2.2 脉冲压缩处理仿真

设线性调频信号的载频fo=25 MHz,调制频率带宽B=5MHz,采样频率fs=20 MHz,满足中频采样定理要求,脉冲宽度τ=60μs,目标距离12 km,时间延迟![]() 脉冲重复周期为320μs,信号幅度A=l。一个脉冲采样点数为L=Tfs=1 200,线性调频信号的时宽带宽积即脉宽压缩比D=300,则输出脉冲宽度r'=60μs/300=200 ns。

脉冲重复周期为320μs,信号幅度A=l。一个脉冲采样点数为L=Tfs=1 200,线性调频信号的时宽带宽积即脉宽压缩比D=300,则输出脉冲宽度r'=60μs/300=200 ns。

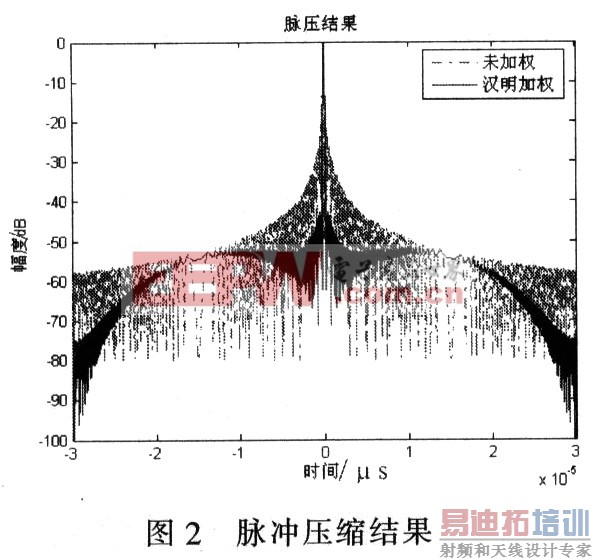

由以上参数产生的线性调频信号的目标回波信号,经正交相干检波产生的I/Q两路信号抽取。最后进行匹配滤波的各个过程的MATLAB仿真,脉冲压缩结果如图2所示。从图2看出,脉冲压缩后产生窄脉冲,输出波形具有辛格函数性质.除主瓣外。在时间轴上还有延伸的一串副瓣。另外还可看出.经过海明加权后的第一副瓣比主瓣下降约40 dB,而主瓣宽度也相应拓展,比没有加权的脉冲压缩结果理想许多。

[p]

[p]

3 逻辑设计和仿真

3.1 分布式算法的硬件结构

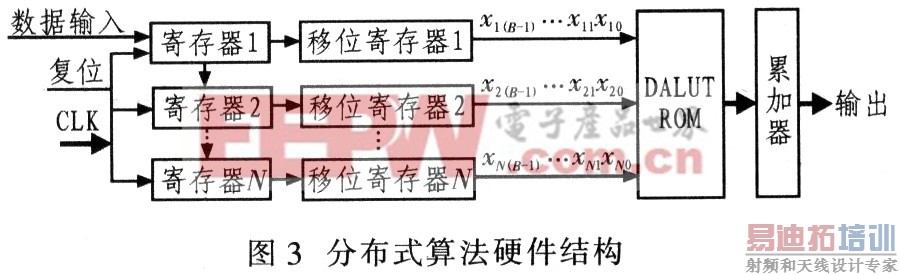

根据分布式算法原理得出采用FPGA实现的分布式算法的硬件结构,如图3所示。

图3中N为该模块的滤波器阶数,那么DALUT有2N个存储单元,如果滤波器抽头数过多,查找表规模随抽头数的增加成指数递增。因此实现高阶滤波器时,要分割查找表。因为卷积运算是线性的,所以在将每个子表的输出相加可得到总输出。逻辑设计是基于Altera公司的Stratix系列FPGA为平台,在OuartusII软件中利用VHDL语言和原理图进行逻辑设计。

3.2 5阶FIR滤波器设计

Stratix器件的LPM_ROM模块最少有32(25)个存储单元,所以设定滤波器模块阶数N=5。5阶滤波器模块设计如图4所示,其中lpm_dff0为12位锁存器,5个锁存器对输入数据进行移位寄存,firda5为分布式算法模块,DATAS[11:0]输出引脚是滤波器模块最后一个锁存器输出,作为滤波器模块级联时不同滤波器模块之间的数据移位。

分布式算法模块firda5实现数据的并串转换、DALUT查表、加权累加。设计中采用状态机实现分布式算法的状态转移,这样简化计算过程,在实现算法时发挥关键作用。根据分布式算法的状态转移关系,每输入一个数据,在下一个数据输入之前,需要在状态s1停留12位数据宽度的时钟时间和2个寄存的时钟时间(在QuartusII软件中,器件选用Stratix系列,利用LPM_ROM模块,地址输入是寄存输入,数据输出也包含寄存器)以及一个数据输出时钟时间:所以系统时钟必须为数据时钟的16倍,图中div 16实现16分频。

3.3 50阶匹配滤波器设计

由于匹配滤波器就是有限脉冲响应(FIR)滤波器,具有线性特性,所以通过低阶滤波器的直接级联相加就可以实现高阶滤波器,前一个滤波器的移位数据DATAS[11:0]作为下一个滤波器模块的信号输入,每个滤波器模块都根据图4设计,只需要根据不同的系数更改DALUT表中的数据。50阶匹配滤波器的逻辑设计如图5所示。其中,Imatch50模块为匹配滤波器复系数实部对应的50阶滤波器,而Qmatch50模块为匹配滤波器复系数虚部对应的50阶滤波器。输出信号包括16位I信号和16位O信号。

[p]

[p]

对该匹配滤波器波形仿真,输入数据为MATLAB仿真的12位数据,由于该滤波器做的是50x50点的卷积.所以输出数据为50+50-1=99个,仿真波形如图6所示。

4 结论

通过仿真分析脉冲压缩过程和调试验验证整个设计.可看出利用基于分布式算法能够大大减少数字脉冲压缩的运算量,提高脉冲压缩效率。由于匹配滤波器的系数是以中心,点对称的,所以可采用线性相位FIR滤波器在FPGA中的实现算法,这样同等性能的滤波器设计可减小一半的硬件规l模。同时,还可通过分时复用嵌入式乘法器来实现卷积,这样就会节省更多的逻辑单元,并且有能力实现更多功能。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:DDS信号源的FPGA实现

下一篇:FPGA在激光测速靶中的应用