- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

一种基于EPLD技术的抗干扰滤波器的实现

1问题的提出

在同步串行数据传输过程中,时钟线上只要有一点小毛刺就会导致数据传输失误,从而影响系统的正常工作。传统的处理方法是在接收端并入一小电容来滤除毛刺,这种方法只能去除某一固定频率下的干扰,而在实际工作中,干扰有可能由多种干扰源混合产生,其频率可能是变化的。另外,若同步串行传输有多个接收端,则需要在每个接收线上都并上一电容,这样,多个电容并联在同一信号线上,势必导致所需的信号失真。随着现代电子技术的发展,EPLD以其编程灵活方便而日益成为现代电子设计的重要手段之一。本文介绍了一种基于EPLD的数字滤波器,它可以抑制某些低频线路上的干扰,利用此滤波器可以阻止某些频带的干扰信号通过,从而起到硬件抗干扰的作用。由于采用了EPLD技术,硬件编程方便、灵活,针对不同的干扰源的特性,可采取相应的措施来解决。

2解决方案

串行传输线在实际传输过程中容易窜入干扰,其形式一般为小毛刺或窄脉冲形式,可利用它与主信号的不同特性加以滤除。

2.1基本工作原理

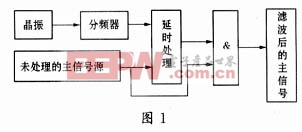

消除干扰信号需两路输入信号:主信号和参考时钟信号。参考时钟信号经过分频、调整脉宽等处理,以此使主信号源产生所需的延时,再与其本身信号相比,从而滤去主信号源上的一些窄波干扰信号。滤波器的原理图如图1所示。器件可采用LATTICE公司的ispLSI1032E,参考时钟信号可采用8M晶振。

2.2具体电路设计

编程软件为LATTICE公司的ispEXPERTSystem,它是一套完整的数字系统设计软件,设计输入可采用原理图输入、硬件描述语言输入、混合输入等方式,并可对所设计的数字电路系统进行功能仿真和时序仿真。

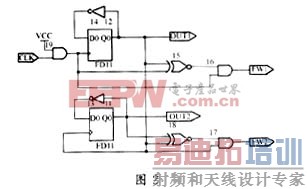

2.2.1分频电路

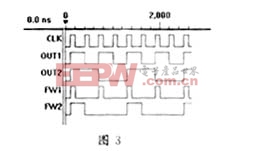

分频电路可根据各具体干扰源的脉冲宽度来确定。具体电路如图2所示,CLK为8M晶振信号,经整形后作为DQ触发器的触发信号,OUT1输出二分频后的4M方波信号,同时作为下一级触发器的时钟信号OUT2输出四分频后的2M方波信号,FW1输出频率为4M、脉宽为125ns的脉冲信号,FW2输出频率为2M、脉宽为250ns的脉冲信号,具体波形如图3所示。由此类推,继续级连DQ触发器即可输出八分频、十六分频信号,脉宽也可视具体情况而作相应的改变,电路类似FW1、FW2的产生电路。

由图2,在ispEXPERT中经仿真得出如图3所示的波形。

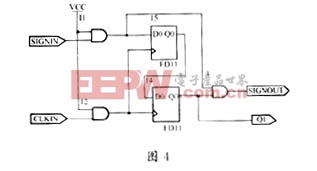

2.2.2延时电路

根据干扰源的情况,以前面所述信号作为触发时钟,未经处理的信号源经触发产生延时,再与其本身相比,这样,一些干扰信号由于脉宽过窄而被滤去。具体电路如图4所示。

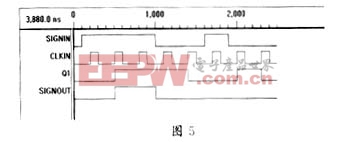

SIGNIN为需处理的信号,被第一个触发器触发后,产生延时,同时送入二级触发器产生二级延时。CLKIN信号的频率可视干扰源的宽度而定,但需注意的是,干扰源的宽度要远远小于信号源的宽度,否则信号宽度将被大幅削减,导致特性被破坏。电路仿真波形如图5所示。

在SIGNIN信号线上,第二个脉冲由于其宽度小于CLKIN信号周期而被滤去。这在同步串行传输的时钟线上显得尤为重要。

3效果分析

此电路简单可靠,笔者在一串行同步通讯过程中运用此电路解决干扰问题,取得了良好的效果。

由于基于EPLD技术,不需额外增加硬件,且编程灵活,可在ispEXPERT中直接仿真,节省了大量的实验时间。但在实际操作中需注意两点:一是在运用此滤波器时,主信号脉冲会有一定的延时,作为同步时钟,此延时对串行通讯不会有太大的影响,但若在数据线或其它信号线上运用时,需考虑延时时间对系统的影响;二是在运用ispEXPERTSystem进行编程时,它提供的宏器件功能与TTL器件相似,但个别引脚有差别。另外,针对各种传输线上的干扰,可根据上述原理加以推广应用。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...