- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

可在线升级的FPGA并行配置方法的实现

在当今变化的市场环境中,产品是否便于现场升级、便于灵活使用,已成为产品进入市场的关键因素。而基于 SRAM结构的 FPGA器件的出现,为系统设计者动态改变运行电路中的逻辑功能创造了条件,也为现场升级等奠定了基础。但由于 SRAM的掉电易失性,系统每次上电时,必须重新配置数据,只有在数据配置正确的情况下系统才能正常工作。

笔者在实际项目应用中,采用 SST89V564微处理器对 FPGA进行快速高效的 PPA数据配置,不仅可以完成对 FPGA的上电启动配置,同时利用其 IAP技术还可以在 FPGA配置完以后,通过修改微处理器中的配置数据和参数来实现系统的在线升级。

1.FPGA的 PPA配置过程

FPGA的在线配置方式一般有两类:一是通过下载电缆由计算机直接对其进行配置;二是通过微处理器对其进行配置。前者调试时非常方便,在应用现场是很不现实的,只适合产品的调试,而一般实际产品中采用微处理器对 FPGA进行配置。

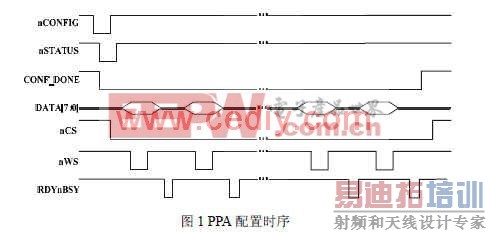

FPGA器件 PPA配置时序如图 1所示,其中 nCS和 CS两个片选信号只需用一个,当

选用 nCS作为片选信号控制配置,CS接高电平。其配置过程为微处理器在 nCONFIG引脚上产生一个最少 21µs的低脉冲,等待直至 nSTATUS和 CONF_DONE变低。此时将 nCONFIG置高, nSTATUS会在 nCONFIG跳高后 4µs内跳高,则表示 FPGA可以配置了[1]。

配置成功时,FPGA器件释放 CONF_DONE信号,由外部将其拉高。如果微处理器检

测到该信号为高,则表明配置成功;否则,要对其重新配置。

2.基本硬件组成

2.1 SST89V564RD及接口设计

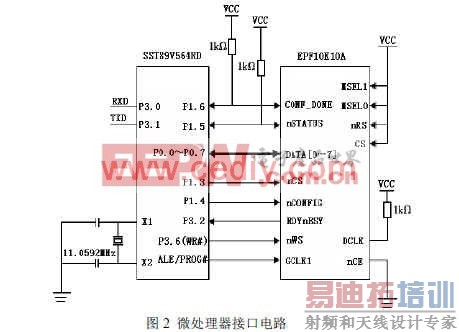

SST89V564RD是 SST公司的 8位集成 SUPERFLASH 存储器的 51 兼容 MCU,带有 1K字节片内 RAM和 72K字节片内 SUPERFLASH。其片内 Flash分成 Block0(64K字节)和 Block1(8K字节)两块,Block0和 Block1低 8K地址相同,程序运行时,可通过设置特功能寄存器 SFCF对低 8K字节的 Flash程序存储块进行切换,以使程序运行在 Block0或 Block1。微处理器与 FPGA的接口电路如图 2所示。

[p]

[p]

2.2 SST89V564RD微处理器片内 Flash应用划分

SST89V564RD微处理器片内 Flash两块( 64K+8K)中, Block1分成 64个扇区,每个扇区包括 128个字节,总共 8K字节;Block0分成 512个扇区,每个扇区包括 128个字节,总共 64K字节[2]。

微处理器两块 Flash地址应用划分为: Block0中,低地址段 0x0000~0x1FFF存放对 Block1进行擦写的 IAP程序,高地址段 0x2000~0xFFFF存放 FPGA配置数据。 Block1的所有空间用来存放上电启动时对 FPGA进行配置以及配置完后的 IAP操作程序。微处理器默认下从 Block1启动。当程序运行在 IAP命令状态时,可以通过设置特功能寄存器 SFCF使程序运行在 Block0或 Block1,来对另一 Flash块进行擦写或升级。

由于 Block0和 Block1的低 8K字节的地址相同,因此在编程应用程序到 Flash中时,编程器将 Block1的地址定义在 0x10000~0x11FFF地址段,在编译程序时需要将 Block1的程序定位在 0x10000~0x11FFF之间才能正确烧写。

3.软件设计

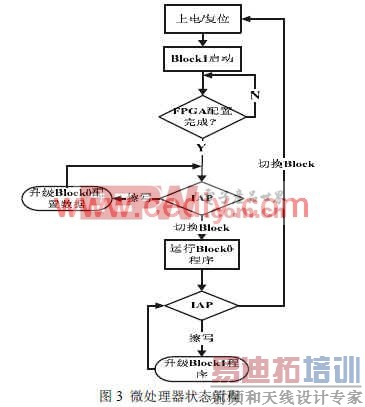

微处理器状态流程如图 3所示,在上电启动时,微处理器从 Block1启动,读取 Block1中 0x2000开始的配置数据,完成对 FPGA的配置。配置完成以后,微处理器处于 IAP状态,既可以通过串口 IAP指令来对 Block0高地址段的 FPGA配置数据进行擦写或升级,也可以通过串口 IAP指令切换微处理器跳到 Block0中低地址段运行,来对 Block1中的程序进行擦写或升级。

由于 Block0中低地址段存放的只是对 Block1进行擦写的 IAP程序,因此无需擦写或升级该部分程序。升级只限于当更改 FPGA逻辑功能时升级 Block0高地址段的配置数据,或者更改了 FPGA芯片时更改 Block1中的配置数据参数以及 Block0中高地址段的配置数据。当程序运行在 Block0中,要切换到 Block1运行重新配置 FPGA时,将产生复位信号,复位微处理器和 FPGA使微处理器重新对 FPGA进行配置。

[p]

硬件电路的设计只提供了接口工作的内核和基础,只有在软件的控制下,接口才能发挥作用,硬件电路与软件程序是紧密相关的 [4]。本设计中 FPGA采用 Altera公司的 EPF10K10ATC144-3,含有 576个逻辑单元和 6144个RAM位,其配置数据大小为 15000Bytes,微处理器给EPF10K10ATC144-3的配置程序如下:

unsigned char FpgaConfig(void)

{

unsigned int iConfigDataByteCount;

unsigned char code * pConfigDataAddress;

pConfigDataAddress = 0x2000; //FPGA 配置数据的起始地址

nCONFIG = 0;

while((nSTATUS==1) || (CONFIG_DONE == 1));

nCONFIG = 1;

while((nSTATUS==0);

iConfigDataByteCount = 0;

CFG_CS_ = 0;

while(CONFIG_DONE == 0)

{

while(RDYnBUSY == 0);

FPGA_CFG_ADDRESS = *pConfigDataAddress;

pConfigDataAddress++;

iConfigDataByteCount++;

if ((iConfigDataByteCount > 0x3A98) || ( nSTATUS==0) )

//EPF10K10ATC144-3 配置数据为0x3A98(15000)字节,升级成相同封装和引脚的

//EPF10K30ATC144-3 时,只需将0x3A98 改成0xC63E(50750)即可

{

CFG_CS_ = 1;

return ERROR;

}

}

CFG_CS_ = 1;

return SUCCESS;

}

在不更改硬件板的条件下,若更改 FPGA芯片升级系统,升级成含有 1728个逻辑单元和 12288个 RAM位的 EPF10K30ATC144-3芯片时,由于与 EPF10K10ATC144-3具有相同的封装和引脚排列[3],因此硬件上可以直接更换 FPGA芯片来升级,而软件上只需将 Block1程序中对 FPGA配置的数据大小参数 15000改成 50750(见上程序注释)。而升级芯片的配置数据,则直接通过串口 IAP将配置数据写入 Block0高地址段即可。因此,能非常方便的在线完成 FPGA内部逻辑甚至更换 FPGA芯片时的系统升级。

4.结论

本文给出了基于 SST89V564RD处理器的 FPGA被动并行异步配置的软硬件实现,该方法充分利用了 SST89V564RD的 IAP技术以及分块大容量的 Flash存储技术,能快速、方便、灵活地对对 FPGA的内部逻辑功能进行在线升级,还可以完成在升级相同封装和引脚的 FPGA芯片时,进行整个系统的在线升级。本方法也适合于其他类似的微处理器。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...