- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的两路视频同步播放系统的设计

1、引言

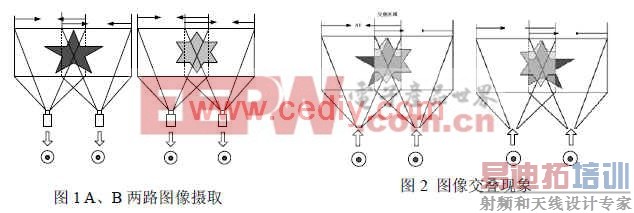

如图 1所示,两台摄像机C1、C2分别对具有部分重叠区域的景物进行拍摄。在 t1时刻拍摄,得到了图像A1、B1;在下一时刻t2,得到了图像A2、B2。

在同一屏幕上重现原图像时,必须保证两个播放器依次同时播放图像 A1和B1,A2和B2,以保证图像经拼接后正常显示。由于两路视频播放器各自具有独立性,因此在读取、解码等过程中都会出现不同程度的不同步。如图 2所示,两路图像由于播放的不同步将发生交叠现象。因此,为了避免图像交叠现象的发生,必须对两路视频同步播放问题进行研究。

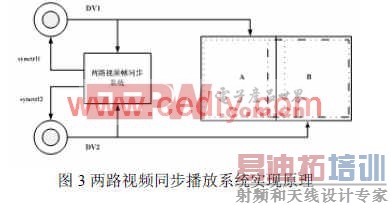

如图 3所示,本系统实现两路视频信号同步播放的原理是:基于图像重叠部分的相关信

息,通过一定的同步检测算法判定两路播放视频是否同步并检测出两路视频相差的帧数,再通过对播放器的调整使两路视频同步播放。

2、硬件系统设计与搭建

已经有研究表明两路视频信号在 PC机上的同步播放是可实现的,而本系统则是利用嵌入式系统来实现同步播放。接下来,本文将对基于嵌入式系统的两路视频同步播放系统的设计、搭建以及调试进行展开。 [p]

2.1 硬件系统总体设计

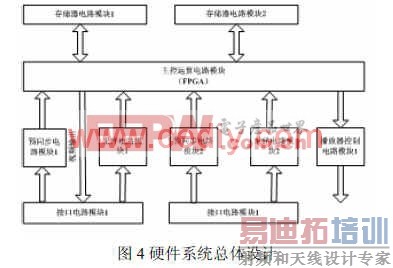

如图 3.1所示,两路视频同步播放系统由接口电路、输入视频信号预同步电路、输入视频信号重叠区域图像采样窗电路、数据存储电路、主控运算及播放器控制电路组成。

2.2 主要硬件功能模块电路设计与测试

2.2.1 接口电路模块设计

接口1和接口2分别将两路视频信号由播放器引入后续处理模块,并将处理后的视频信号输出给显示系统。

2.2.2 预同步电路模块设计两路输入视频信号在进行同步处理前需要首先进行缓冲,以期在同一时刻到达主控模块上一致。本系统采用两片有 FPGA芯片控制的 FIFO芯片分别实现两路信号的预同步功能。

本系统采用uPD42280芯片。 uPD42280是容量为256kbyte*8bit (262, 224 * 8bit)的高速场存储器。CMOS动态电路实现了芯片的高速和低功耗。 uPD42280O可以设置为同步或异步读写的FIFO。其中, DI0-7为数据输入,DO0-7为数据输出;/WE、/RE分别为写使能和读使能; /WRST、/RRST分别为写复位和读复位; VDD、GND分别为电源和接地。而在进行预同步处理时,两路输入的视频信号均为隔行PAL制黑白信号,其中亮度信号为8位,即每帧图像大小为702*288*8/1024/8=198Kbyte,所以 uPD42280的容量足够一场图像的存储。 [p]

2.2.3重叠区域采样电路模块设计输入视频信号重叠区域采样窗模块是由两块uPD42280芯片串联构成。通过 FPGA对uPD42280芯片发出控制信号,达到对指定像素区域进行采样的目的。之所以采用两片 uPD42280芯片串联是考虑到系统设定的同步范围。对于 50HZ的PAL制的隔行扫描图像,每一场的采样像素点为32*32=1024个,只取其中 8位Y信号,则每一场的采样数据量为 28800字节。uPD42280场存储器的单片容量为 256K字节,可以容纳约 256场。这样采用两片串联增加了一倍的容量,采样窗的数目可以达到512场。

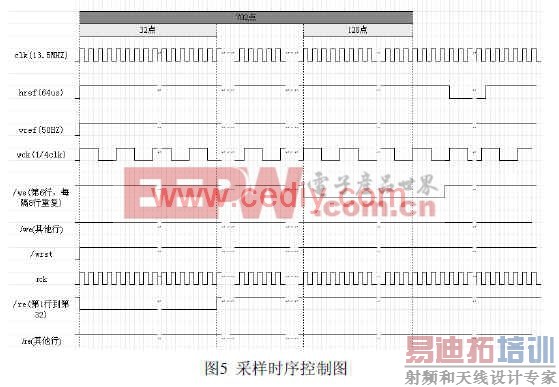

采样的控制时序图5所示,为了对 702*288的右1/4重叠区域进行行列的均匀采样,每隔 8行在后128点进行 1/4clk均匀抽样,得到 32点。同时,每场一共抽取 32行,这样 FIFO中存储数据为32*32=1024byte。而读时钟在每场的前 32行,采用clk(13.5MHZ)进行连续读取。图 6为一帧图像重叠区域采样的效果图。

2.2.4存储器电路模块设计

在本系统中,由于需要用到大规模的图像数据存储及运算存储操作,并且考虑到系统算法的可扩展性,存储器选取了两片 SDRAM芯片 HY57V641620HG,每片 HY57V641620HG大小为 4bank*1M*16bit。在结构设计方面,由于 SDRAM不能够同时进行读写操作,与主控运算电路采取并行连接的方式。这样做的目的是可以进行 SDRAM的乒乓读写操作,提高数据读取及写入的效率。

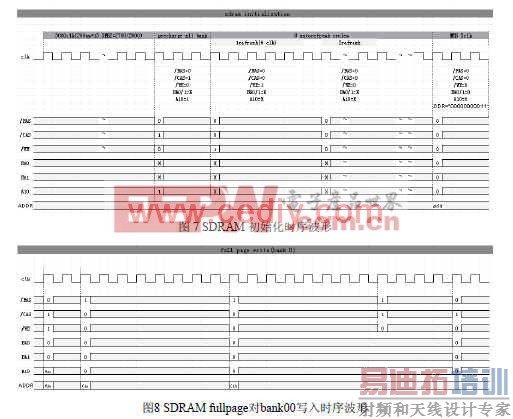

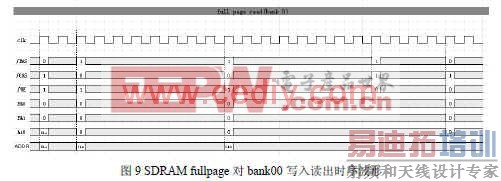

FPGA对SDRAM的初始化和fullpage模式下的读写控制的时序如图 7、8、9。

2.2.5 FPGA主控运算电路模块设计主控运算电路是本系统中最重要的硬件组成部分,因为这部分电路将承担整个系统大部分控制和运算任务。这部分电路由 FPGA芯片 EP1C6及其附属电路组成。 [p]

EP1C6属于ALTERA公司的Cyclone系列,内含 5980个逻辑单元;内部 RAM大小为 92160bit;支持 LVTTL, LVCMOS, SSTL-2, 和SSTL-3 I/O 标准;支持 66和 33-MHz, 64- and 32-bit PCI 标准;支持高速 640 Mbps) LVDS I/O和低速 (311 Mbps) LVDS I/O;支持311-Mbps RSDS I/O;支持外部存储器,包括 DDR SDRAM (133 MHz),FCRAM, 和SDRAM;支持 IP核。它具有20块M4K,可实现乘法器的数量为 7。本系统采用的封装形式为 240-Pin PQFP,可用的I/O口为185个。两路视频同步播放系统需要近170个I/O口、连接 SDRAM和植入算法,而 EP1C6可以提供足够多的逻辑单元资源。

2.2.6 电源电路模块及其他电路设计播放器控制电路由开关芯片CD4066构成。CD4066芯片是4路双向 CMOS开关电路,可用于数字和模拟信号的信号传输和复用。

主控运算电路中的Cyclone EP1C6芯片需要接 3.3V和1.5V两种电压,存储器 HY57V641620HG芯片需要接3.3V电压, Upd42280芯片和CD4066芯片需要接 5V电压。所以在设计电源电路部分时考虑需要满足3.3V、1.5V、5V三种电压。系统选择的电源芯片为固定3.3V和1.5V两个型号的SPX1587芯片。 SPX1587芯片具有静态电路低的特点,在满负载的情况下电压降仅有1.1V。 3、结论

本文作者创新点在于应用嵌入式系统解决以往使用 PC机解决的视频同步播放问题。本硬件系统充分考虑到了两路视频同步播放算法的各种硬件功能需要,进行了各硬件电路模块的设计、搭建及调试。硬件平台的基本功能──显示、采样及存储器的控制均达到同步播放算法的要求。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:基于FPGA的VGA时序彩条信号实现

下一篇:40nm工艺带来全新竞争力