- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

关于PCB设计阻抗控制方面的建议(下)

W(设计线宽)该因素一般情况下是由客户决定的。

但在PCB设计时请充分考虑线宽对该阻抗值的配合性,即为达到该阻抗值在一定的H、Er和使用频率等条件下线宽的使用是有一定的限制的。

当然阻抗控制不仅仅是上述几因素,上面所提的只是比较而言影响度较大的几因素,也是从PCB制造厂商的角度来看待该问题的。

以下是我们在高多层PCB实际生产加工过程中,总结出来的一些高多层PCB的结构示例,但必须说明的是:

这仅仅是一点,不足以说明一面的问题,仅仅是建设性的参考。

由于时间和篇幅的限制在此处没能将一些目前已经成为趋势的做法列出如内层使用H/H(半 Oz )铜箔、Low DK材料……

其中的一些数值是比较粗略的计算结果,实际运用时还需根据实际的情况进行细化。

考虑到客户的需求基本上还是——高多层能薄一点,因此在高层的结构中我们尽可能的举厚度比较适中的结构。

20层以上由于结构更加复杂,同时是客户与我们共同努力的结果,因此在实际加工的过程中,根据客户的具体要求再做具体的探讨。如24层 6mm、30层6--8mm…...

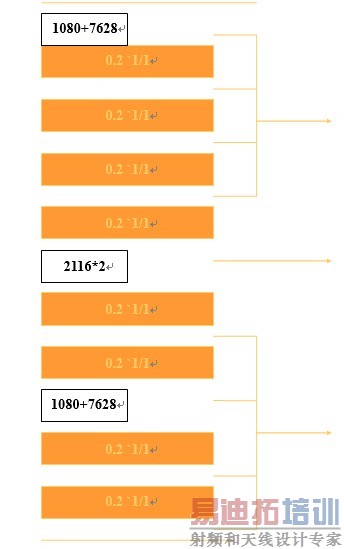

2.0mm 8层PCB板的通常配置

1080+7628

1080+7628

1080+7628

1080+7628

其阻抗值一般为两种情况:

Microstrip Line=8mil Zo=70 左右

Offset Stripline 有两种可能:

1. Line=8mil Zo=45 左右

2. Line=8mil Zo=50 左右

3. 如为背板的设计则还有另一种情况

针对不同的需要可以对左示的结构进行更改而得。

3.0mm 8层PCB板的通常配置

1080+7628*2

7628*2

7628*2

1080+7628*2

其阻抗值一般为两种情况:

Microstrip Line=8mil Zo=80 左右

Offset Stripline 有两种可能:

1. Line=8mil Zo=58 左右

2. Line=8mil Zo=68 左右

3.如为背板的设计则还有另一种情况

针对不同的需要可以对左示的结构进行更改而得。

2.0mm 10层PCB板的通常配置

1080+7628

7628+1080

1080*2

7658+1080

1080+7628

其阻抗值一般为以下几种情况:

Microstrip Line=8mil Zo=70 左右

Offset Stripline 有两种可能:

1. Line=8mil Zo=33 左右

2. Line=8mil Zo=47 左右

3.如为背板的设计已经调整内部地电的排列还有其他的一些情况出现。

针对Stripline Zo偏小的情况一般是压缩Microstrip 的介质厚度来增加Stripline的介质厚度满足Zo的需求。

针对不同的需要可以对左示的结构进行更改而得。

2.0mm 12层PCB板的通常配置

1080*2

1080*2

1080*2

1080*2

1080*2

1080*2

其阻抗值一般为以下几种情况:

Microstrip Line=8mil Zo=50 左右

Offset Stripline 有两种可能:

1. Line=8mil Zo=30 左右

2. Line=8mil Zo=33 左右

3.如为背板的设计以及调整内部地电的排列还有其他的一些情况出现。

针对Stripline Zo偏小的情况一般是增加Stripline的介质厚度满足Zo 的需求,通常50ohm的需求该种板会在3.0mm厚度。

针对不同的需要可以对左示的结构进行更改而得。

3.0mm 14层PCB板的通常配置

1080+7628

1080+7628

1080+7628

1080+7628

1080+7628

1080+7628

1080+7628

其阻抗值一般为以下几种情况:

Microstrip Line=8mil Zo=70 左右

Offset Stripline 有两种可能:

1. Line=8mil Zo=33 左右

2. Line=8mil Zo=40 左右

3.如调整内部地电的排列还有其他的一些情况出现。

针对Stripline Zo偏小的情况一般是缩小Microstrip 的介质厚度,同时缩小地地或电电之间的介质厚度来增加Stripline的介质厚度满足Zo的需求,包括采用不同厚度芯板进行压合的方法。

针对不同的需要可以对左示的结构进行更改而得。

16层 3.0mm电路板的结构

1080+2116

1080+2116

2116*2

2116*2

2116*2

2116*2

1080+2116

1080+2116

其阻抗值一般为以下几种情况:

Microstrip Line=8mil Zo=60 左右

Offset Stripline 有几种可能:

当Line=8mil时 Zo值在33--50…

如调整内部地电的排列还有其他的一些情况出现。

针对Stripline Zo偏小的情况一般Backboard设计 Top&Bom层是无Microstrip 要求,因此调整它们的介质厚度,调整地地或电电之间的介质厚度来增加Stripline的介质厚度满足Zo 的需求,包括采用不同厚度芯板进行压合的方法。

针对不同的需要可以对左示的结构进行更改。

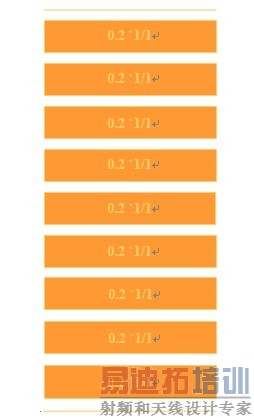

18层 3.0mm厚度电路板的结构

各层之间的半固化片全部使用1080*2

从此种结构的特性上来看Microstrip

Line=8mil Zo=50 左右比较符合常规要求,但Offset Stripline 则可能太小。

针对Stripline Zo偏小的情况,一般Backboard设计 Top&Bom层是无Microstrip 要求,因此调整它们的介质厚度,调整地地或电电之间的介质厚度来增加Stripline的介质厚度满足Zo 的需求。

包括采用不同厚度芯板进行压合的方法通过局部的调整来满足要求。

针对不同的需要可以对左示的结构进行更改。

18层 3.8mm厚度电路板的结构

1080+7628

2116*2

1080+7628

从此种结构的特性上来看Microstrip Line=8mil Zo=70 左右,比一般常规的要求偏大,但Offset Stripline 则可能偏小。

针对Stripline Zo偏小的情况,一般Backboard设计 Top&Bom层是无Microstrip 要求,因此调整它们的介质厚度,调整地地或电电之间的介质厚度来增加Stripline的介质厚度满足Zo 的需求。

包括采用不同厚度芯板进行压合的方法通过局部的调整来满足要求。

针对不同的需要可以对左示的结构进行更改。

20层 3.0--3.2mm厚度电路板的结构

各层之间的半固化片全部使用1080*2

此种结构阻抗的状况和调整方法与18层3.0mm的情况基本相同,主要的问题是Stripline偏小。

20层 4.0mm左右厚度电路板的结构

标注的地方为1080+2116,其馀的结构为1080+7628

从此种结构的特性上来看,一般情况是属于backboard的设计因此Microstrip就没了,Offset Stripline 的Zo=33--50(依旧设计的层次排列)如想得到50则在设计上一定要处理好一些问题,且并非每个信号层都能控制到。

针对不同的需要可以对左示的结构进行更改。

为使有阻抗要求的PCB在生产加工过程中能得以顺利的完成,故我们建议双方在合作的过程应中注意以下几方面的协作和沟通。

如贵公司的PCB有阻抗控制的要求,则贵公司在提供电路板加工资料时请提供有阻抗要求的该线条的位置、设计线宽、阻抗值、相对应的介质层厚度……相关的参数。

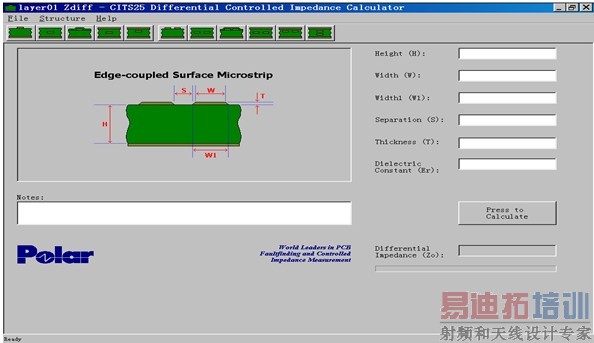

如为差动阻抗还需提供差分线之间的间距。

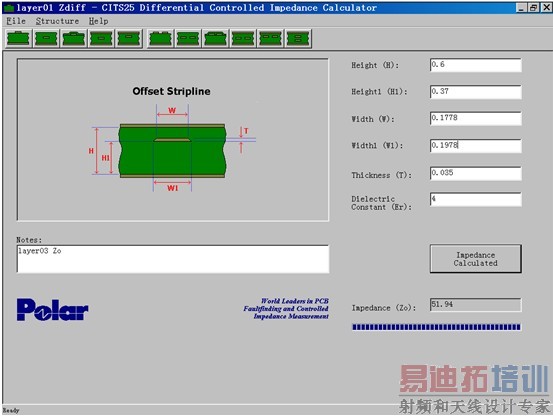

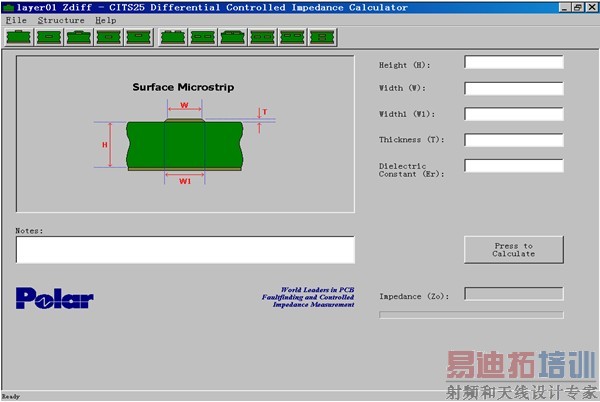

我们收到贵公司的资料之后,将用POLAR CITS25软体进行核算,如发现有偏差,我们将及时通知客户,同时在取得客户同意的条件下对上述各参数进行调整以达到满足阻抗值的要求。

如该PCB其本身的性能是比较特殊的如:RF(射频)板等,在资料中敬请予以说明,因为该类板是不能以改动线宽来满足阻抗值的。

以上所述仅是我们处于PCB制作厂商的角度,对阻抗的加工、品质控制方面的一些浅薄认识,其必然有很多疏漏之处,敬请谅解。

“阻抗控制”在PCB业界来讲是一个比较复杂,相对较新的课题,因此在合作的过程中,相互的交流、协作是第一性的,我们忠实于客户的设计,但不局限。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:PCB多层板设计规范

下一篇:印刷电路板设计布局指导原则(中)