- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

印刷电路板设计布局指导原则(下)

7、数位IC的削尖电容(despikingcapacitor)

数位IC旁的削尖电容其特质为频宽高915-150MHz)、容量小(470-1000pF),目的在于提供IC开关时的瞬间脉冲电流。削尖电容并非越大越好,符合上述条件的最小电容,即是最佳选择,尽量少用大于0.1mF的电容。数位IC的频率越高,则电容越小。0.lmF电容用在高达l5MHz的系统频率,若超过l5MHz以上,就使用0.0lmF的电容。高频宽、低电感的碟状陶瓷电容(diskceramiccapacitor)或是多层陶瓷电容(multilayerceramiccapacitor)适合用来做为IC间的削尖电容。DRAM由于需要refreshcharge,因此需要较大的削尖电容,通常256K的DRAM需要0.lmF的削尖电容。

尽可能将电容靠近IC摆置,Vcc和GND脚位在晶片的对面端之标准会形成对EMI敏感的回路,如果IC的电源端靠近则回路是相当小的,图12说明一个典型逻辑IC的电容摆置,把电容放在Vcc和GND的中间位置。

8、电源线滤波器(PowerLineFilter)

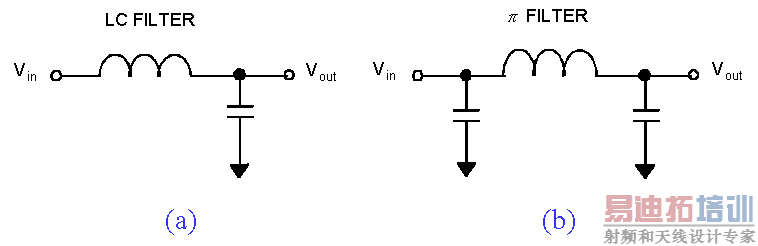

如果需要进一步滤除电源线的噪音,可使用LC或p滤波器(图13),尽量将滤波器靠近元件,而将其它的信号绕线在滤波器的附近。

图13.电源滤波器

陶铁磁珠(ferritebead)也可用来滤掉不想要的系统高频噪音[Ott,1988,pp.152-156],它们提供一种较便宜的方式来增加高频衰减,但对直流或低频信号则不会造成信号的衰减,对于消除lMHz以上的噪音最为经济有效。陶铁磁珠的阻抗通常低于l00Ω,主要应用于低阻抗的电源电路,如电源供应器、C级功率放大器、谐振电路与SCR开关电路等。如果单珠未能有效滤除高频噪音,也可将多珠串连或多绕几圈,但须注意圈数的增加,将提高杂散电容,这对高频噪音的滤除是不利的。陶铁磁体珠子是圆柱形且能在导体上滑动,用在电源供应器时,应将磁珠靠近PCB的电源输出端,如图14所示。

图14.抑制高频噪音的ferritebead安置于电源供应器PCB的电源输出端

9、信号布局

电源线与地线布局完之后,接下来的就是信号线的布局了。在布局数位和类比混合信号的PCB时,勿将数位和类比信号混杂,电路板上的数位电路、类比电路、以及易产生噪音的电路应予以区隔,8如图所示。试着先绕线最为敏感的线路,并去除电路间的藕合路径。通常与数位电路或噪音产生电路介面的低阶类比电路最容易受到干扰,在绕线时应格外谨慎。

10、数位电路的噪音与布线

类比电路的噪音通常来自于电路板的外部,然而数位电路的噪音则往往由内部产生,因此如何降低内部噪音是数位电路板布线的首要考量因素。在MCU为主的系统中最敏感的信号是时序、重置和中断线路,震荡器在开机时尤为敏感。千万不要将这些线路与高电流开关线路平行,如此易于被电磁交互藕合信号破坏。此效应容易破坏MCU经由中断码的执行,引起非预期的重置或中断。时序信号受到干扰,将造成失相(losephase)使整个系统失去同步,由于MCU的执行是依据适当的时钟脉波,因此不要期望它们能在EMI的干扰下恢复正常操作。

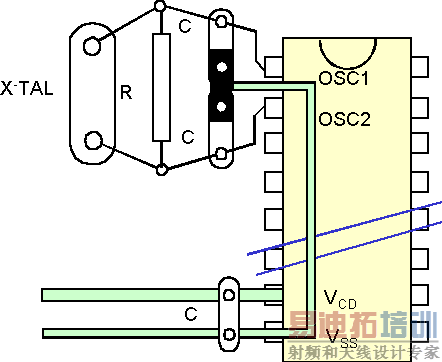

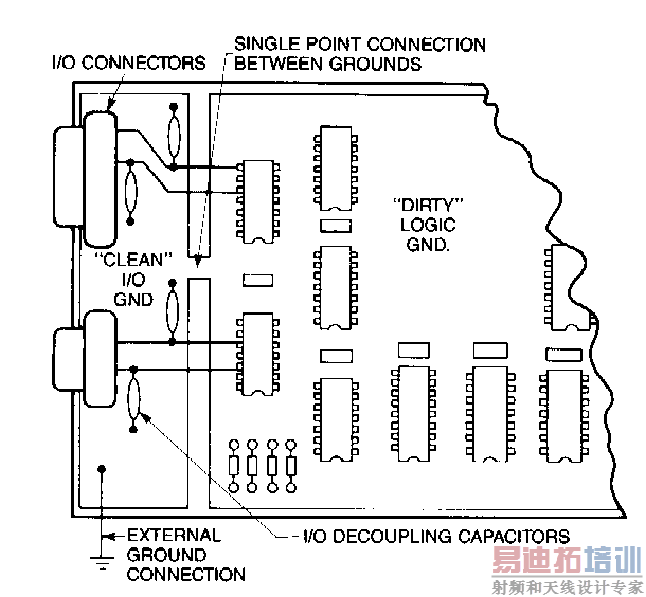

震荡器或陶瓷共振时钟是一种RF电路,必须绕线以减少它的发射位准及敏感性。图15以一个震荡器或陶瓷共振器与DIP包装的例子来说明,尽量将震荡电路的配置靠近MCU,若是震荡器或陶瓷共振器的本体很长,就放在PCB之下并将包装接地。如果震荡器在PCB之外,就将MCU放在离PCB连接器的附近,不然,就将MCU尽量摆近震荡器以缩短绕线距离。震荡线路的地线应该连接元件可能使用最短绕线的接地脚位,电源和接地脚应该直接绕线到PCB的电源部分。图16说明PCBj挈b的 /FONT>I/O接地与I/O电缆线的解藕电容布线方式。

11、类比电路的噪音与布线

低阶信号(low-levelsignal)容易受到数位信号的干扰;如果类比和数位信号必须混杂,要确定彼此的线路相交成90度角,这将会降低交互藕合(crosscoupling)的效应。

如果类比电路的signalreference未与数位线路隔离的话,类比-数位转换器的信号会受到严重的干扰,因此不可将数位电源和接地直接输入类比-数位转换器的signalreference线路。这些脚位应直接绕线自母板的电源端之参考电压,此电压参考脚位应用lK欧姆的电阻和l.0mF电容来滤波。

图15.石英或陶瓷共振电路的线路布局

图16.PCB『干净的I/O』接地与I/O电缆线的解藕电容布线方式

四、PCB设计布局降低噪音的检查要项

以下列出在量产线路板之前的详细检查表,这些检查项目是集合市场经验以及实作应用的经典[Montrose,1996;Ott,1988]。

1、抑制噪音源

在符合设计规格的前提下,使用最低频率的时钟以及最和缓的上升时间。

如果时钟电路在电路板外,则将相关之时序电路(如MCU)靠近连接器,否则,就放在母板中间。

将震荡器平放于PCB并接地。

尽可缩小时序信号的回圈区域。

将数位I/O驱动器(digitalI/Odriver)放置于PCB外缘。

将进入PCB的信号予以适当滤波。

将离开PCB的噪音信号予以适当滤波。

使用碟状陶瓷电容(diskceramiccapacitor)或是多层陶瓷电容(multilayerceramiccapacitor)做为数位逻辑IC的削尖电容。

尽量将数位IC之despikingcapacitor靠近IC旁边。

使用排线包装的OP放大器,将"+"端接地,以"-"端作为输入信号端。

提供适当的突波阻尼(surgeabsorber)给继电器线圈。

使用45度角(圆弧更佳)的绕线以取代90度角来减少高频辐射。

如果需要,在产生高频噪音的电源线用feed-throughcapacitor连接外部。

如果需要,在产生高频噪音的电源线串接陶铁磁珠(ferritebead)以滤除高频噪音。

将shieldcable两端均接地(但并非作为地线),以降低电磁辐射。

2、减少噪音藕合

如果经济许可,使用多层电路板来分开PCB上不同性质的电路。4层板PCB,通常外面的两层为信号,中间两层为电源层(powerlayer)与地线层(groundlayer)。如电路板为数位类比混合电路,应将数位与类比的跑线分别布线,最后再将地线予以单点连接。

对单层及双层线路板使用单点电源和接地的布局。如采用双层线路板制作以微处理器为基础的控制板(数位类比混合电路),则应特别注意数位与类比电路『电源线』与『地线』的布局。

选用晶片组以缩短时序的传输线。

将digitalI/O晶片组安置于PCB边缘并靠近连接器。

高速逻辑闸仅限用于特定功能之电路。

对电源和接地使用宽绕线。

保持时序绕线、汇流排和晶片致能与I/O脚位和连接器分隔开。

尽量将数位信号线路(尤其是时钟信号)远离类比输入和电压参考脚位。

当与混合信号转换器并用时,勿将数位和类比线路相交,信号的绕线要彼此远离。

分隔噪音与低阶类比信号脚位。

将时序信号与I/O信号垂直绕线。

将时序电路远离I/O信号线。

尽量使敏感脚位的长度越短越好。

用宽扁的绕线处理重要的线路,并在绕线的每一边采用接地保卫环。

勿将敏感的信号线与高电流、快速交换信号并行。

缩短解藕电容的脚位长度。

高频线路应保持短而直接。

缩短时序与其他周期性信号的绕线长度。

避免绕线于震荡器和其它对噪音极度敏感的电路之下。

过滤任何进入包含敏感线路的信号线。

当低阶信号与噪音脚位位于同一个连接器上时,例如扁状电线(flatcable),尽量将之分离并以地线置于其间。

避免低阶(low-level)、低频(low-frequency)电路的接地回路(groundloop)。

将噪音线扭绞(twisted)以抵消相互间之藕合与电磁辐射。

使用所有IC内的电源和接地脚位,勿空接。

3、降低噪音吸收

尽量避免任何信号回圈,否则就减少回圈范围。

分隔信号、噪音和硬体电源和接地。

使用可选择频率的滤波器来应用。

连接所有未用到的输入到电源或接地。

在所有的类比参考电压加旁路电容。

将管状电容(tubularcapacitor)的外围箔片接地。

将电解电容并联一个高频电容。

对高效率类比及混合信号ICS不要使用IC座。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...