- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

半导体封装的连续性测试

随着半导体封装越来越复杂,常用的连续性测试不再适合开路及引脚间短路的检测了,因为大部分测试方法是针对沿着封装周边器件的引脚来设计的。然而,现今的微表面贴装器件(SMD)和球栅阵列(BGA)封装的引脚是按阵列方式排列的,这种排列需要使用新的测试方法。

在典型的测试中,测试设备对所有引脚并联,施加小量电流(通常几毫安),并测量每个引脚的二极管导通电压,以此验证测试仪与内部芯片之间的连续性。为每个引脚的预期二极管压降设定适当限值,一次并联的连续性测试就能够从开路的I/O筛选元件。这种并联连续测试同样能够检测短路的I/O引脚,但条件是短路引起的引脚输出电压与典型二极管压降有差别,例如,接地或处在高电压状态。但是,在遇到短路产生的电压差不够大时,并联测试则是无效的。

为了筛选这种短路,可以采用其他参数测试或功能测试,然而采用这种间接方法时,存在一定的风险。在器件定型和生产的测试步骤已确定的情况下,将会失去间接筛选某些短路引脚的能力。另外,当相邻的I/O引脚功能没有呈现很大差异时,间接连续性测试不能检测出短路,例如两个输出通道供电分开但稳压源相似时。

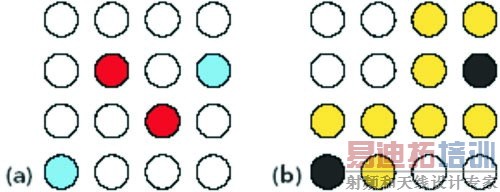

图1 a) 栅格配置产生引脚—引脚短路的多种可能性。

b) 红色引脚可能与8个粉红色引脚短路。

c) 黑色引脚接在,对白色I/O引脚测试连续性,测试设置可检测I/O引脚的水平和对角线短路。

d)改变黑色和白色引脚设置可检测垂直短路。

显然,需要使用不同的测试方法,以保证全部被测元件的引脚之间没有短路的可能性。解决方案要考虑到阵列的复杂性以及二维的I/O配置不会明显增加测试时间和成本。现今封装类型的阵列配置极大地增加了两个或更多引脚相互短路的可能性,因为在封装中部的引脚可能与它周围的任何引脚发生短路。然而,对两个相邻I/O引脚的每种组合都作连续性短路测试,在生产中是不现实的,特别是在I/O数目增加的情况下。

黑和白的连续性测试法

一种被作者称为“黑和白”连续性测试法,这种技术是在使用自动测试设备(ATE)检测引脚短路和开路与不牺牲测试效率之间作出折衷。黑和白连续性测试,试图采用最小的测试条件集,来检测封装上两个或更多引脚之间的全部潜在短路。

在常用引脚至引脚的连续性测试中,测试迭代与I/O计数有关。对于一个m x n的I/O阵列来说(其中m是行数,n是列数),检测全部潜在的短路需要(m x n)-1次迭代。对于典型的ATE,当I/O计数超过100的单独连续性测试时间可能超过1秒。但是,黑和白连续性的测试时间只要几十毫秒,而且与I/O引脚数无关。并且只有在测试不能切换至接地的引脚时,这种测试方法才要增加时间。

对于图1a所示的配置,两个相邻引脚的短路可出现多种不同的情况。每个完全被包围的引脚至少有八种可能的短路发生(见图1b中红色引脚)。一种很费时间但保证ATE可测试每种可能短路的方法是,强迫全部粉红色引脚I/O连接到低电位。出现短路时,测试仪将测得红色引脚是低电压而不是二极管导通电压。这种过程需要对其余I/O引脚反复进行,直至覆盖全部可能性为止,显然对具有大数量的引脚器件来说,这种方法并不可取。

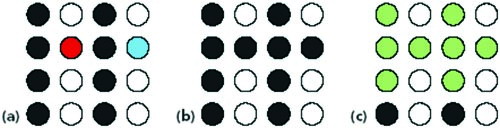

图2 a) 在16个I/O引脚配置中有多个电源(红色)和接地I/O引脚。

b)器件的接地I/O引脚设置为地电位,对所有白色(非相邻)和黄色(相邻)引脚测试连续性。

黑和白连续性测试法采用测试程序板的数组作驱动,效率要高得多。为了对每个引脚与相邻脚做全面的开路或短路测试,黑和白测试法只要三次连续性测试迭代,并与SMD和BGA的封装所拥有的I/O引脚数量无关。这种方法甚至可应用到多行多列的内嵌式封装,例如高引脚计数的无引线框架式封装(LLP)。

第一次连续性测试是全部引脚并联的开路迭代测试。如果任何一个引脚开路,则此项测试失败。第二次迭代测试(图1c)是ATE驱动黑色引脚接地和测试白色引脚。此项测试是检查在对角线或水平的相邻引脚之间出现的短路,而不检查垂直的相邻引脚的短路。第三次迭代(图1d)处理最后的情况。虽然黑和白测试法试图减小迭代至三次,但不可避免会出现要求更完整覆盖迭代的情况。一种情况是由电源和接地I/O引脚所引起,另一种主要是测试硬件接入被测器件的方法所引起。

多路供电和接地

电源引脚通常用作电流源来测试,以保证测试的连续性。另一方面,接地引脚通常用作连续性测试的参考。某些设计不主张强迫接地引脚的电位高于其它I/O引脚,因为会引起某些电路反向偏置并且损坏芯片。因而,测试电源引脚和接地之间的开路和短路则要求有计划地进行。

考虑图2a的I/O配置,图中红色I/O引脚是电源和蓝色I/O引脚是接地。测试连续性时必须首先分辨哪些I/O引脚是电源,哪些是接地,然后执行黑和白测试步骤。首先,对全部并联引脚作开路测试。之后,强制全部接地引脚为低电位。注意接地引脚与相邻引脚(黄色)之间有任何短路将导致连续性测试失效(见图2b)。

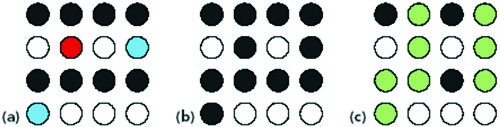

图3 a)黑色引脚接地,对白色I/O引脚测试连续性。红色和蓝色引脚由于内部芯片的互连已经接地,如图b)的黑色引脚所示。c)绿色引脚表示非可测短路。

图4 a)水平接地配置可检测垂直短路。

b)器件配置的电源引脚和接地引脚分别共同连接在一起。

c)绿色引脚表示在垂直方向的非可测短路。

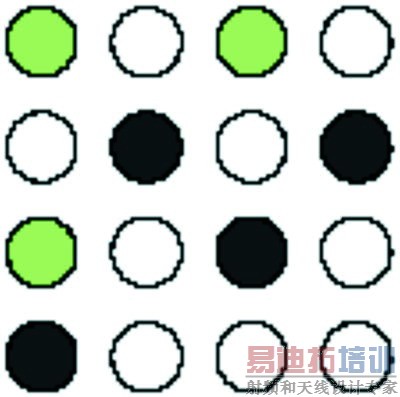

图5 a)逻辑“与”运算最少可确定一个与相邻I/O引脚的非可测短路。b)逻辑“非或”运算确定最后一组引脚的最少一个与相邻I/O引脚的非可测短路。

图6 最后测试步骤是将电源和接地引脚全部接地,测试绿色I/O引脚的连续性。

继续对相隔各行施加低电位和测量其余引脚的连续性(见图3a)。由于器件芯片的电源和接地都是分别连接在一起,有效配置表现为图3b所示的形式。第二次迭代可检测到全部白色I/O引脚的所有水平和对角线短路。然而,对于少数组合是无法检测出短路的引脚。水平或对角线的相邻引脚的短路是不能测出来的,如图3c的绿色引脚所示。

将垂直的黑色(接地)I/O引脚切换到水平引脚(见图4a),第三次迭代检测垂直短路。对连续性测试,最少一个器件的接地设置为低电位。通常由于芯片的电源和接地引脚分别连接在一起,最后的引脚配置如图4b所示。为了检验非可测的引脚,垂直扫描在同一行内被测的但不与黑色引脚相邻的所有引脚。这些非可测引脚用明显的绿色在图4c中示出。

对全部图3c和4c的绿色引脚作“与”运算,能够检测出任何不能用短路测试的引脚。所有黑色和绿色引脚视为逻辑1,而所有白色引脚视为逻辑0。(注意如果两个相应引脚是黑色,则“与”运算结果可以忽略,因为两个这样的I/O引脚在第一次测试时即被检测为短路。这些I/O引脚在本分析中视为冗余引脚。)

最后,对逻辑“与”运算的输出(图5b)和并联连续性测试的配置(图2b)作“非或”运算。在此,测试引脚-引脚短路的最后迭代,设置器件的电源和接地引脚为地电位,然后在非可测引脚短路下测试其余引脚的连续性(见图6)。

由此可见,与检测引脚-引脚连续性的全部15次迭代相比,作者的4次迭代连续性测试法能够检测相邻两个引脚之间的所有可能短路。读者可从网页www.tmworld.com/archives 下载黑和白连续测试法的步骤。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:无铅转移与过渡技术

下一篇:Sn-Ag-Cu无铅焊料的可靠性研究