- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

PCBA大讲堂:QFN 封装的焊接品质

QFN (Quad Flat No leads,四方平面无引脚封装)在现今电子业界的IC封装当中似乎有越来越普遍的趋势,QFN 的优点是体积小,足以媲美CSP(Chip Scale Package)封装,而且成本也相对便宜,IC的生产制程良率也蛮高的,还能为高速和电源管理电路提供较佳的共面性以及散热能力等优点。此外,QFN 封装不必从四侧引出接脚,因此电气效能更胜引线封装必须从侧面引出多接脚的SO等传统封装IC。

尽管QFN 有这么多的封装及使用上的优点,但它却给电路板组装厂带来不少的焊接品质冲击,因为QFN 的无引脚设计,一般很难从其外观的焊锡点来判断其焊锡性是否良好,虽然QFN 的封装侧面仍留有焊脚,但有些 IC 封装业者只是把 Leaf frame(导线架)切断露出其切断面,并没有再加以电镀处理,所以基本上吃锡就不太容易,再加上保存一段时间后切断面容易氧化,更造成侧面上锡的困难。

▼QFN 的侧面焊脚为导线架(lead frame)的切断面,并无电镀层。

QFN 吃锡标淮

其实在 IPC-A-610D, Section 8.2.13 Plastic Quad Flat Pack No Leads (PQFN ) 的规范中,并未明确定义QFN 的侧边吃锡一定要有平滑的圆弧形曲线出现。

There are some package configurations that have no toe exposed or do not have a continuous solderable surface on the exposed toe on the exterior of the package and a toe fillet will not form.

也就是说QFN 的焊接其实可以不用管侧边的焊接状况,只要确保QFN 焊脚底部及正底部的散热片位置真正的吃锡部份就可以了。QFN 底部焊脚的吃锡其实可以想像成 BGA,所以建议应该可以参考 IPC-A-610D, Section 8.2.12 Plastic BGA 的标淮,至于中间接地焊垫的吃锡可能得视各家的设计而定。

▼ QFN 侧边焊脚吃锡虽然不好,但因为其底面吃锡良好,所以电气特性仍然良好。

▼ QFN 侧边焊脚吃锡良好。

QFN 焊锡性检查及测试

就如同 BGA 的焊锡检查标淮,目前QFN 的焊锡检查除了用电测 (In-Circuit-Test 、 Function Test) 来侦测其功能之外,一般也会佐以光学仪器或 X-ray 来检查其焊锡的开、短路不良现象。老实说 X-Ray 的等级不够好的话,还真的不是很容易检查出来QFN 的焊锡问题。如果无论如何还是找出焊锡性的问题,最后只能使用切片(Micro-section)或 用渗透染红试验 (Red Dye Penetration Test)查看BGA焊锡等破坏性实验来检查。

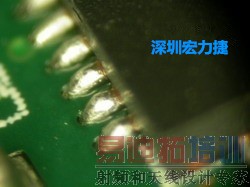

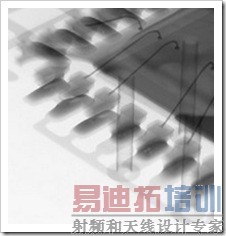

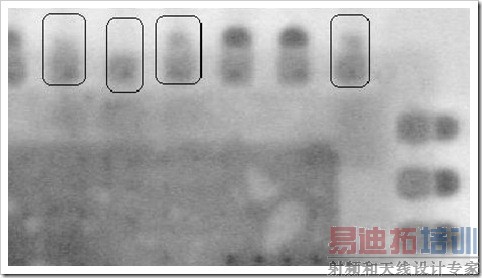

▼这张图片来自网路,使用 X-Ray 检查QFN 焊锡。

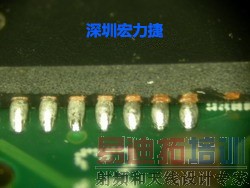

▼这张图片来自网路,使用 X-Ray 检查QFN 焊锡,疑似焊接不良。

QFN 空焊的可能解决方法

当发现QFN 空焊时应该先澄清是否为零件氧化问题,可以把零件拿去作一下沾锡性实验来作确认,再来要判断是否有固定焊脚空焊的问题,一般接地脚比较容易产生空焊,可以考虑变更电路板的布线设计,在电路板的线路(trace)上增加热阻(thermal relief)垫来减少焊脚大面积直接接地的比率,这样可以延缓热量散失的速度。(所谓「热阻」就是把接地的线路宽度缩小,让热能不要马上传导到整片的接地大铜片。)

也可以试著调整炉温(reflow profile),或改为斜升式回流焊曲线(slumping type)以减少锡膏在预热时吸收过多热量的问题。

参考阅读: SMT加工回流焊的温度曲线 Reflow Profile

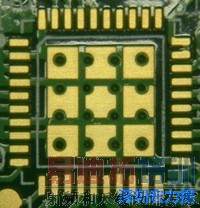

曾经发现有QFN 底部中间的接地焊垫上印刷过多锡膏,当零件流过回流焊时造成零件浮起形成空焊的问题,这时候可以考虑将QFN 底部中间的接地焊垫印刷成「田」字型会比整片印刷要来得好,过回流焊时也较不会因锡膏全部熔融成一团而造成零件浮动的情形。

另外电路板的焊垫上尽量不要有导通孔(vias),中间散热接地垫上的通孔(vias)也要尽量塞孔,否则容易影响焊锡量及气泡的产生,严重的还可能导至焊接不良。

▼ 通孔(vias)塞孔

加「氮气」是否可以有效增加QFN 的良率?我只能说见仁见智,氮气是可以防止零件氧化,但能否焊上QFN 的侧面焊脚,还是有待观察,况且加氮气会增加成本,还是摆在最后再考虑就好了。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...