- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

时序计算和Cadence仿真结果的运用

摘要:本文通过对源同步时序公式的推导,结合对SPECCTRAQuest时序仿真方法的分析,推导出了使用SPECCTRAQuest进行时序仿真时的计算公式,并对公式的使用进行了说明。

一、前言

通常我们在时序仿真中,首先通过时序计算公式得到数据信号与时钟信号的理论关系,在cadence仿真中,我们也获得了一系列的仿真结果,怎样把仿真结果正确的运用到公式中,仿真结果的具体含义是什么,是我们正确使用Cadence仿真工具的关键。下面对时序计算公式和仿真结果进行详细分析。

二.时序关系的计算

电路设计中的时序计算,就是根据信号驱动器件的输出信号与时钟的关系(Tco——时钟到数据输出有效时间)和信号与时钟在PCB上的传输时间(Tflytime)同时考虑信号驱动的负载效应、时钟的抖动(Tiitter)、共同时钟的相位偏移(Tskew)等,从而在接收端满足接收器件的建立时间(Tsetup)和保持时间(Thold)要求。通过这些参数,我们可以推导出满足建立时间和保持时间的计算公式。

时序电路根据时钟的同步方式的不同,通常分为源同步时序电路(Source-synchronous timing)和共同时钟同步电路(common-clock timing)。这两者在时序分析方法上是类似的,下面以源同步电路来说明。

源同步时序电路也就是同步时钟由发送数据或接收数据的芯片提供。图1中,时钟信号是由CPU驱动到SDRAM方向的单向时钟,数据线Data是双向的。

图2是信号由CPU向SDRAM驱动时的时序图,也就是数据与时钟的传输方向相同时的情况。

图中参数解释如下:

- Tft_clk:时钟信号在PCB板上的传输时间;

- Tft_data:数据信号在PCB板上的传输时间;

- Tcycle:时钟周期

- Tsetup':数据到达接收缓冲器端E1时实际的建立时间;

- Thold':数据到达接收缓冲器端E1时实际的保持时间;

- Tco_max/Tco_min:时钟到数据的输出有效时间。

由图2的时序图,我们可以推导出,为了满足接收芯片的Tsetup和Thold时序要求,即Tsetup'>Tsetup和Thold'>Thold,所以Tft_clk和Tft_data应满足如下等式:

Tft_data_min>Thold-Tco_min+Tft_clk (公式1)

Tft_data_max<Tcycle-Tsetup-Tco_max+Tft_clk (公式2)

当信号与时钟传输方向相反时,也就是图1中数据由SDRAM向CPU芯片驱动时,可以推导出类似的公式:

Tft_data_min>Thold-Tco_min-Tft_clk (公式3)

Tft_data_max<Tcycle-Tsetup-Tco_max-Tft_clk (公式4)

如果我们把时钟的传输延时Tft_clk看成是一个带符号的数,当时钟的驱动方向与数据驱动方向相同时,定义Tft_clk为正数,当时钟驱动方向与数据驱动方向相反时,定义Tft_clk为负数,则公式3和公式4可以统一到公式1和公式2中。

三.Cadence的时序仿真

在上面推导出了时序的计算公式,在公式中用到了器件手册中的Tco参数,器件手册中Tco参数的获得,实际上是在某一种测试条件下的测量值,而在实际使用上,驱动器的实际负载并不是手册上给出的负载条件,因此,我们有必要使用一种工具仿真在实际负载条件下的信号延时。Cadence提供了这种工具,它通过仿真提供了实际负载条件下和测试负载条件下的延时相对值。

我们先来回顾一下CADENCE的仿真报告形式。仿真报告中涉及到三个参数:FTSmode、SwitchDelay和SettleDelay。其中Cadence时序仿真的结果是通过SwitchDelay和SettleDelay两个参数反映出来的。

在解释FTSmode、SwitchDelay和SwitchDelay前先解释一下BufferDelay曲线的含义。BufferDelay曲线是Cadence仿真器断开实际负载,带上驱动芯片器件手册提供的测试负载条件下获得的一条曲线。测试负载是在IBIS仿真模型库中设置的。Cadence仿真报告中的延时测量是以BufferDelay为基准曲线,以V Measure为起始测量点获得的相对延时值。

- FTSmode:定义了当前仿真驱动器的特性,分为Fast、Type和Slow。该三种特性是在IBIS模型中定义的,Fast是驱动器沿最快的模式,Slow是驱动器沿最慢的模式,从而定义了驱动器在正常工作条件下的两种极限特性。

- SwitchDelay: 定义为SwitchDelayFall和SwitchDelayRise两者的最小值。图3给出了SwitchDelayFall和SwitchDelayRise的图形解释。

- SwitchDelayFall:是从BufferDelay下降沿的Vmeasure点开始到接收波形下降曲线第一次穿过高电平阈值时的延时值。

- SwitchDelayRise:是从BufferDelay上升沿的Vmeasure点开始到接收波形上升曲线第一次穿过低电平阈值时的延时值。

- SettleDelay:是SettleDelayFall和SettleDelayRise两者的最大值。图3给出了SettleDelayFall和settleDelayRise的图形解释。

- SettleDelayFall:是从BuferDelay下降沿的Vmeasure点开始到接收波形上升曲线最后一次穿过高电平阈值时的延时值。

从SwitchDelay和SettleDelay的定义我们可以看出,SettleDelay是一个与输入端的建立时间(Tsetup)有关的量,SwitchDelay是一个与输入端保持时间有关的量(Thold)。

公式1和公式2中的Tft_data与Tft_clk在Cadenee仿真工具中是通过仿真获得的数据,它与Cadence仿真中fast和slow状态下的SwitchDelay与SettleDelay参数有关。

为了了解Cadence仿真中的SwitchDelay和SettleDelay与时序公式中参数的关系,我们重新分析一下包含有BufferDelay曲线的时序图。

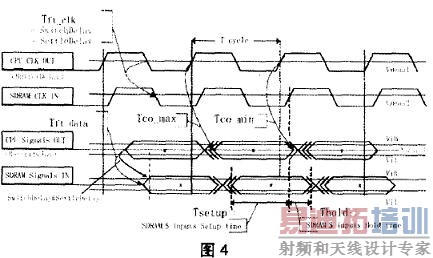

在图4中,时钟输出和数据输出使用的是BufferDelay曲线,此时Tco是时钟BuferDelay曲线和数据BufferDelay曲线之间的延时关系,这种定义符合“手册中的Tco是在特定负载下测得的”说法。

在图4中,CPU CLK OUT(BuferDelay)和CPU Signals OUT(Buferdelay)是在测试负载条件下的信号输出波形(对应于图3中的BuferDelay曲线,而不是驱动端输出曲线),SDRAM CLK IN和SDRAM Signals IN是在实际负载条件下输入端口的仿真波形。

在器件手册中给出时序关系时,对于时钟信号,通常以某一测量电压为时间测量点,如图4中的Vmeas1和Vmeas2,对于驱动端测量电压点为驱动器件手册中定义的测量点,对于接收端测量电压点为接收器件手册中定义的测量点。在Cadence仿真时,对于接收端电压测量点的设置,通常在接收器件模型中,把输人高低门限电平定义成Vmeas2来实现。对于驱动端电压测量点的设置,是在驱动器件模型参数中设置的。此时对于时钟仿真的结果是,时钟信号的SettleDelay和SwitchDelay值相等。

对于数据信号的测量点就稍微有点复杂了,这要根据手册中Tco的测量方式来确定,有的器件手册Tco是从时钟的Vmeas到数据的Vmeas来测量的,有的手册是从时钟的Vmeas到数据的门限电平来测量的。如果采用从时钟的Vmeas到数据的门限电平来测量的,则在Cadence仿真中,要对高低电平门限分别作为测量点仿真,然后取最恶劣的仿真结果。

对于公式中数据的延时Tft_data,从Cadence仿真中对SettleDelay和SwitchDelay的定义和图4中的时序关系可以看出,Tft_data就是仿真结果中的SettleDelay和SwitchDelay参数,并且SettleDelay是与建立时间(Tsetup)有关,SwitchDelay是与保持时间(Thold)有关,因此公式中的Tft_data_min对应仿真结果中的SwitchDelay,Tft_data_max对应仿真结果中的SettleDelay,考虑到通常Slow状态的延时比Fast状态的延时要大,因此,公式中的Tft_data_min对应仿真结果中Fast状态的SwitchDelay,Tft_data_max对应仿真结果中Slow状态的SettleDelay。

对于公式中时钟的延时,从测量方式中可以看出Tft_clk=SettleDelay=SwitchDelay,考虑到同一公式中仿真状态的一致,因此,公式中与Thold有关的不等式中的Tfl_clk对应于Fast状态的仿真值,与Tsetup有关的不等式中的Tft_clk对应Slow状态的仿真值。写成公式就是:

Tft_data_fast_switchdelay>Thold口Tco_min+Tft_clk_fast (公式5)

Tff_data_slow_settledelay<Tcycle-Tsetup 口Tco_max+Tft_clk_slow (公式6)

在实际仿真中,我们只要保证仿真结果满足公式5和公式6的时钟和数据关系,也就保证了单板工作时序的正确性。

四.总结

Cadence公司的Allegro SI和SigXplor设计工具为硬件开发工程师提供了一个功能强大的高速PCB仿真手段,通过仿真设计,可以设计出符合要求的信号时序和信号完整性,从而提高单板和系统的工作稳定性,降低开发风险和开发成本。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:在Protel

DXP中建造自己的原理

库

下一篇:PowerPCB使用经验