- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

PWM 控制系统中的电磁兼容设计

电磁兼容性是脉宽调制( PWM) 控制系统的重要指标。系统中由于功率电路主开关器件的快速导通和关断,导致功率电路电流变化率di/dt 、电压变化率du/dt 较大。它们在布线电感上产生很大的尖峰电压,叠加在开关器件两端,严重威胁开关器件的安全;另外,由于分布电感和分布电容的耦合作用,它们又会耦合到系统控制电路逻辑器件的输入端,造成控制电路误动作,使系统工作异常,甚至不能工作。因此,PWM控制系统对电磁兼容设计要求较高,其电磁兼容性设计应与系统设计同步进行,从方案论证阶段开始,直至设计定型,都应采取电磁兼容性设计措施。

1 PWM控制系统的基本组成

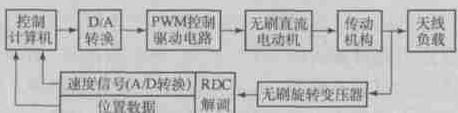

PWM控制系统的组成如图1 所示。

图1 PWM伺服控制系统组成

该系统为由无刷直流电动机驱动的机载雷达伺服系统。系统由位置传感器(无刷旋转变压器) 、位置与速度检测解调单元、A/D 转换电路、D/A 转换电路、PWM控制驱动电路、无刷直流电动机等部分组成,系统的位置与速度校正运算则由控制计算机完成。

2 电磁干扰的产生与传递途径

系统中形成电磁干扰必须具备以下3 个基本条件:存在干扰源;有对干扰敏感的接收单元;有耦合通道,即能把干扰能量从干扰源耦合到敏感接收器上、并使系统明显恶化的介质中。在系统设计中,只要消除了其中一个因素,干扰就能被抑制。

PWM控制系统中的干扰源主要有:

a) 驱动器中功率电路的开关元件在开关过程中,大脉冲电流的切换引起的干扰,其di/dt 很大,不仅影响驱动电路,而且还会通过电源、地进入控制电路。

b) 电动机启动、制动时,在负载突变处产生瞬变电压,其振幅会高于电源电压,而且前沿陡峭、频带很宽,经由直流电源进入控制电路。

在PWM控制系统中,许多部件、元器件都会成为被干扰的敏感单元。但接收干扰必须同时具备两个条件:干扰源的信号电平超过了电子部件的容许范围;干扰源的信号频率可以被电子部件响应。

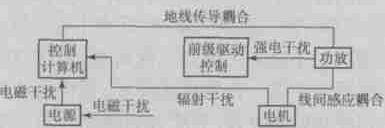

图2 PWM控制系统中干扰的主要传递途径

PWM控制系统中的敏感单元主要有PWM开关器件驱动接口电路、数字电路及微处理器、传感器等。PWM控制系统中主要干扰传递途径(见图2) 有:

a) 传导耦合。通过电源线、地线、信号线将干扰引入敏感单元。

b) 公共阻抗耦合。传递信号需要一个公共基准点即电位参考点,这就形成了公共阻抗,流入公共阻抗的电流便将干扰耦合到其他电路中,不良的接地方式是引起公共阻抗耦合的主要原因。

c) 辐射耦合。载荷导线或元器件会辐射电磁场,因而元器件与元器件之间、导线与导线之间、导线与元器件之间会通过分布电容或互感产生感应电压。

d) 线间感应耦合。若线间距离较小,信号大时会产生线间耦合。

3 电磁干扰的抑制

3. 1 元器件的合理布局与印制电路板的布线设计

设计系统时,应在初步设计阶段进行电磁兼容性分析,选用不易产生干扰及对干扰不敏感的元器件和电路,同时对元器件和电路进行合理布置,以减小相互影响, 并便于采取防护措施。元器件可选用标准CMOS 器件,以减小印制板的干扰。印制板上的元器件可按电原理图的顺序排列,使各部分功能明确,并力求元器件安排紧凑,一般应以某个元器件为中心来进行组合布局,这样可使走线最短。

设计印制板时,尽量选用多层板,可将数字电路和模拟电路分开,安排在不同层。尽量使敏感元器件远离干扰源,例如功率电路中的主开关器件就属于强干扰源,而滤波器、低电平放大器、微处理器及接口电路是弱信号部分,设计时两者应尽量远离。尽量把干扰源单独布置在一层,并远离敏感电路。如果系统内的数字电路分为高速、中速和低速电路,可在印制板设计时使上部为高速数字电路,中部为中速电路,下部为低速电路。布线应尽可能短,尤其在高频电路中。印制导线的拐角应成45°或圆角,因为直角或尖角在高频电路和布线密度高的情况下会造成信号质量、时序、电磁干扰问题。高速电路输入及输出所用的走线应尽量避免相邻或平行,以免发生回授,在这些走线之间最好加接地线。时钟信号引线很容易产生电磁辐射干扰,布线时应靠近地线,不能把它长距离与信号线平行走线。为避免信号线之间的串扰,两条信号线切忌平行,而应

采取垂直交叉方式或拉开两线之间的距离,也可在两条平行的信号线之间增设一条地线,以减小交叉干扰。

印制板设计中应尽量采取“井”字网状布线,即一面横向布线,另一面纵向布线,以减小寄生耦合。在印制电路板上还应尽可能多地保留铜箔作地线,这样得到的屏蔽效果比一长条地线要好,其传输线特性和屏蔽作用将会得到改善,并能起到减小分布电容的作用。设计中还应注意根据印制板中电流的大小,尽量加粗电源线宽度,以减少环路电阻。

3. 2 地线的妥善处理

地线对电磁兼容性影响相当大。PWM 控制系统包含电动机、功率电路、模拟电路、数字电路、传感器等。系统中的模拟地作为运算放大器、比较器、APD 转换器、DPA 转换器中模拟电路的零电位;数字地作为系统中各数字电路的零电位,应与模拟地分开,以避免模拟信号受数字脉冲干扰;信号地为传感器(例如旋转变压器等) 或前置放大的地线;功率地是电动机、功率电路等大电流装置的地线;机壳地包括机架、机壳、屏蔽罩等。系统地是各种地的最终回流点,直接与大地相连;交流地是交流电源的零电平参考点,交流地上很容易产生各种干扰,因此交流地不能与其他地线连接。

正确处理上述地线,是PWM 控制系统电磁兼容设计的重要环节,直接影响到控制系统的可靠性。系统中可将地线分为以下4 组,每组信号自成回路,以减少公共阻抗耦合。

a) 敏感信号及小信号电路地,包括低电平电路、A/D 转换电路、D/A 转换电路等;

b) 不敏感信号和大信号电路地,包括高电平电路、末级驱动放大器等;

c) 干扰源地,包括电动机、功率电路等;

d) 机壳地。

系统最终采用串、并综合一点接地。

3. 3 屏蔽、滤波措施的正确利用

对于辐射干扰和电磁耦合性干扰,切断其传播途径的有效措施是屏蔽,凡是对系统构成干扰源的设备和部件都应将其屏蔽。一般可用双绞线作为信号引线,以减少电磁感应,并且使各个小环路的感应电动势呈反向抵消。也可使用电缆,其抗干扰效果较好,但要注意电缆屏蔽层的接地,因为电缆屏蔽的作用主要是由屏蔽层接地产生的。

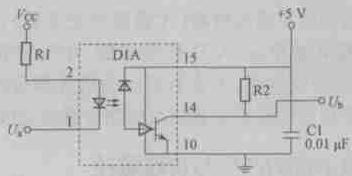

传导途径造成的干扰主要通过滤波技术加以解决。PWM伺服控制系统中,电流检测信号含有交流分量,可加一个低通电流滤波环节,放大器的输出电路中也可加低通滤波器滤除高次谐波。对于数字电路,可用整形电路抑制尖峰噪声、毛刺、寄生振荡等;用积分电路去除窄脉冲噪声,也可用软件方法抑制噪声。强电与弱电可用光电隔离器加以隔离,以减小强电对弱电信号的干扰。图3 所示为PWM 伺服控制系统中的实际光隔隔离电路。

图3 用光电隔离器隔离强电与弱电部分

合理使用高频去耦电容可去除高达100 MHz 的高频成分。陶瓷片电容或多层陶瓷电容的高频特性较好。设计印制板时,每个集成电路的电源、地线之间都要加一个去耦电容。去耦电容有两个作用:一是集成电路的蓄能电容能提供和吸收该集成电路开门或关门瞬间的充放电能;二是可旁路掉该器件的高频噪声。

数字电路中典型的去耦电容值为0. 1μF ,有5 nH 分布电感,其并行共振频率约7MHz ,也就是说,对于10 MHz 以下的噪声有较好的去耦作用,对40 MHz 以上的噪声几乎不起作用。对于1μF、10μF 电容,其并行共振频率在20 MHz 以上,去除高频噪声的效果会好一些,在电源进人印制板的地方放一个10μF 的去高频电容且并联0. 1μF 的去耦电容,对抑制干扰往往是有利的。在PWM驱动电路的H 功率桥电源与地之间还应并联电容较大的钽电容器,以抑制尖峰干扰。

3. 4 软件抗干扰措施

应将硬件和软件结合起来抑制电磁干扰。软件抗干扰的主要手段有:数字信号多次读入,保证每次采样信号绝对一致;数字信号多次读出;输入模拟量的数字滤波处理。数字滤波方法很多,需要注意的是应该根据实际信号特性来选择合适的方法。下面是常用的几种数字滤波方法:

a) 算数平均值法。常用于存在周期性干扰的情况,取连续N 个采样数据xi ( i = 1 ,2 , ……, N) 的算数平均值作为输入信号。

b) 滑动平均值法。对于硬件采样速度慢或对采样速度要求高的实时系统,为保证必要的速度,可以将采样得到的N - 1 个数据按时间顺序存放在存储器中,以后每采样一个新数据,就取最新的N - 1 个数据的算数平均值,最后一个旧数据滑出不用。

c) 防脉冲干扰平均值法。由于脉冲干扰的无规律性,可在软件上采取n 次排队取中值方法,以某一采样周期连续采样若干次,从所得的一组数据中去掉认为最不可能的数据,取剩余数据的平均值,便能得到与实际值相近的数据。

d) 一阶递推数字滤波法。软件模拟RC 低通滤波器的一阶递推数字滤波公式为:

Yn = QXn + (1 - Q) Yn - 1 (1)

式中: Xn 为第n 次采样时的输入值; Yn 为第n 次采样时的输出值; Q 为数字滤波器的时间常数,一般取Q=τ/T ;τ为采样周期;1/T 为RC 滤波器3 dB 衰减点。

由式(1) 可达到任意通频带的低通滤波效果。除了上述措施外,还可以采用软件冗余技术,即设置备用程序或设置“软件陷阱”,在程序可能跑飞的空间强行执行一条指令,使程序跳转到程序复位地址。同时,要解决程序跑飞问题,还可加上软、硬件结合的监控定时器即看门狗系统,以及采用软件容错技术,使系统的误动作减少,可靠性提高。

4 结束语

PWM 控制系统中电磁干扰的产生机理和传递途径较为复杂,各种抑制干扰措施的有效性亦随之而异,指望一种既简单又万能的方法是不现实的。但是,电磁兼容性对于PWM 控制系统的电气性能和可靠性影响很大。因此,在产品的方案论证、设计等阶段必须重视电磁兼容性的设计。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...