- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

差分阻抗-什么是差分?

翻译:Michael Qiao

当你认为你已经掌握了PCB 走线的特征阻抗Z0,紧接着一份数据手册告诉你去设计一个特定的差分阻抗。令事情变得更困难的是,它说:“……因为两根走线之间的耦合可以降低有效阻抗,使用50Ω的设计规则来得到一个大约80Ω的差分阻抗!”这的确让人感到困惑!

这篇文章向你展示什么是差分阻抗。除此之外,还讨论了为什么是这样,并且向你展示如何正确地计算它。

单线:

图1(a)演示了一个典型的单根走线。其特征阻抗是Z0,其上流经的电流为i。沿线任意一点的电压为V=Z0*i( 根据欧姆定律)。

一般情况,线对:

图1(b)演示了一对走线。线1 具有特征阻抗Z11,与上文中Z0 一致,电流i1。线2具有类似的定义。当我们将线2 向线1 靠近时,线2 上的电流开始以比例常数k 耦合到线1 上。类似地,线1 的电流i1 开始以同样的比例常数耦合到线2 上。每根走线上任意一点的电压,还是根据欧姆定律,为:

V1 = Z11*i1 + Z11*k*i2 (1)

V2 = Z22*i2 + Z22*k*i1

现在我们定义Z12 = k*Z11 以及Z21 =k*Z22。这样,式(1)就可以写成:

V1 = Z11*i1 + Z12*i2 (2)

V2 = Z21*i1 + Z22*i2

这是一对熟悉的联立方程组,我们可以经常在教科书中看到。这个方程组可以一般化到任意数量的走线,并且可以用你们中大部分人都熟悉的矩阵形式来表示。

图1 各种走线的结构

特殊情况,差分对:

图1(c)演示了一对差分走线。重写式1:

V1 = Z11*i1 + Z11*k*i2 (1)

V2 = Z22*i2 + Z21*k*i1

现在注意在仔细设计并且是对称的情况下,

Z11 = Z22 = Z0,且

i2 = -i1

这将导致(经过一些变换):

V1 = Z0*i1*(1-k) (3)

V2 = -Z0*i1*(1-k)

注意V1 = -V2,当然,这是我们已经知道的,因为这是一个差分对。

有效(差模)阻抗:

电压V1 以地为参考。线1 的有效阻抗(单独来看,在差分对中叫做“差模”阻抗,通常叫做“单线”阻抗)为电压除以电流,或:

Zodd = V1/i1 = Z0*(1-k)

由上可知,因Z0 = Z11 且k = Z12/Z11,

上式可写成:

Zodd = Z11 - Z12

这也是一个在许多教科书中都可以看到的公式。

为了防止反射,正确的端接方法是用一个值为Zodd 的电阻。类似地,线2 的差模阻抗与此相同(在对称差分对的特定情形下)。

差分阻抗:

假定在某一瞬间我们将两根走线用电阻端接到地。因为i1 = -i2,所以根本没有电流流经地。也就是说,没有真正的理由把电阻接地。事实上,有人认为,为了将差分信号和地噪声隔离,一定不能将它们连接到地。因此通常的连接形式如图1(c)中所示,用单个电阻连接线1 与线2。电阻的值是线1和线2 差模阻抗的和,或:

Zdiff = 2*Z0*(1-k) 或

2*(Z11 - Z12)

这就是为什么你经常看到实际上一个差分对具有大约80Ω的差分阻抗,而每个单线阻抗是50Ω。

计算:

知道Zdiff 是2*(Z11-Z12)不是很有用,因为Z12 的值并不直观。但是,当我们看到Z12与耦合系数k 有关,事情就变得清晰了。事实上,耦合系数与我在Brookspeak 中关于串扰的专栏I中谈到的耦合系数是相同的。国家半导体发布的计算Zdiff 的公式II已经被广泛接受:

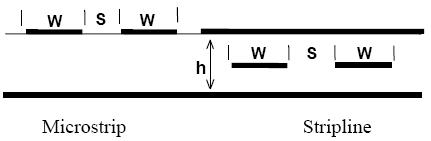

Zdiff = 2*Z0(1-.48*e-.96*S/H) 微带线

Zdiff = 2*Z0(1-.347*e-2.9*S/H) 带状线

其中的术语在图2 中定义。Z0 为其传统定义III。

图2 查分阻抗计算中的术语定义

共模阻抗:

为了讨论完整起见,共模阻抗与上面略有不同。第一个差别是i1 = i2(没有负号),这样式3 就变成:

V1 = Z0*i1*(1+k) (4)

V2 = Z0*i1*(1+k)

并且正如所期望的,V1 = V2。因此单线阻抗是Z0*(1+k)。在共模情况下,两根线的端接电阻均接地,所以流经地的电流为i1+i2 且这两个电阻对器件表现为并联。也就是说,共模阻抗是这些电阻的并联组合,或:

Zcommon = (1/2)*Z0*(1+k),或

Zcommon = (1/2)*(Z11 + Z12)

注意,这里差分对的共模阻抗大约为差模阻抗的1/4。

I "Crosstalk, Part 2: How Loud Is It

" Brookspeak, December, 1997.

II 参考国家半导体"Introduction to LVDS"(第28-29 页),可以从其官方网站上访问:http://www.national.com/appinfo/lvds/。

III 参考"PCB Impedance Control, Formulas and Resources", March, 1998, 第12页。公式为:

本文发表在Printed Circuit Design,一种Miller Freeman 的出版物,1998 年8 月. 1998 Miller Freeman, Inc. . 1998 UltraCAD Design Inc.

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...