- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

IBIS 理解说明

--谨以此文献给初学SI 的艰苦岁月

IBIS 模型在做类似板级SI 仿真得到广泛应用。在做仿真的初级阶段,经常对于ibis 模型的描述有些疑问,只知道把模型拿来转换为软件所支持的格式或者直接使用,而对于IBIS 模型里面的数据描述什么都不算很明白,因此下面的一些描述是整理出来的一点对于ibis 的基本理解。在此引用很多presention来描述ibis 内容(有的照抄过来,阿弥陀佛,不要说抄袭,只不过习惯信手拈来说明一些问题),仅此向如muranyi 等ibis 先驱者致敬。本文难免有些错误或者考虑不周,随时欢迎进行讨论并对其进行修改!

IBIS 模型的一些基本概念

IBIS 这个词是Input/Output buffer information specification 的缩写。本文是基于IBIS ver3.2 所撰写出来(www.eigroup.org/IBIS/可下载到各种版本spec),ver4.2增加很多新特性,由于在目前设计中没用到不予以讨论。。。

在业界经常会把spice 模型描述为transistor model 是因为它描述很多电路细节问题。而把ibis 模型描述为behavioral model 是因为它并不象spice 模型那样描述电路的构成,IBIS 模型描述的只不过是电路的一种外在表现,象个黑匣子一样,输入什么然后就得到输出结果,而不需要了解里面驱动或者接收的电路构成。因此有所谓的garbage in, garbage out,ibis 模型的仿真精度依赖于模型的准确度以及考虑的worse case,因此无论你的模型如何精确而考虑的worse case 不周全或者你考虑的worse case 如何周全而模型不精确,都是得不到较好的仿真精度。

IBIS 模型的构成

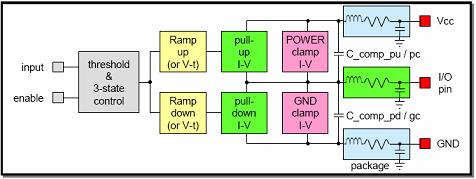

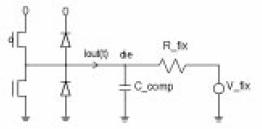

经典示意图如下:

从上图可以看出,基本的IBIS模型包括如下的一些信息(对于不同类型的model有一些信息会省略掉)

VI 曲线: Pullup & Pulldown &POWER clamp& GND clamp

VT曲线: Rise waveform, Fall waveform

还有一些其它比较重要的信息比如Die capacitance: C_comp(最近好像那个muranyi对这个很感兴趣,一直发布presentation讨论怎么把这个做的更精确)以及RLC package parameter。至于一些基本的输入以及使能信息会在软件设置自动生成,不需要我们多关注。对于于ibis模型长什么样子,大家去micron主页ddr2 sdram模块下载几个io buffer看看是什么样。希望你先看看长啥样再看下面的一些说明。

IBIS 的应用场合

任何电路都可以用下面的模型(好像是Shannon 模型我不知道。。。)来描述

Driver -------------interconnect------------------Receiver

注意IBIS 模型描述的是Driver/Receiver 的行为特性而并不是它们的电路特性,因而内部的一些逻辑延时是没有考虑的(在此你就该好好明白为啥要区分Tco的概念),通过使用IBIS 模型,从而得出interconnect 对于电路的影响。在目前一些使用ibis model 仿真的软件中,在Cadence 里面,ibis 模型是转换为dml 格式,在Hyperlynx 里面直接调用ibis 模型。由于ibis 支持的buffer type 很多,每个类型都会有对应的格式以及需要包含的信息,常用有output, input 以及IO 模型,至于其他的模型,大家可以参照ibis 说明,有些些微的差异。

IBIS 模型中vi/vt 曲线的由来

有大牛的示意图形,不多说

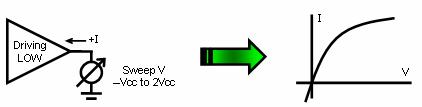

Pull down 曲线由来(此曲线需要考虑与clamp 曲线重复的部分)

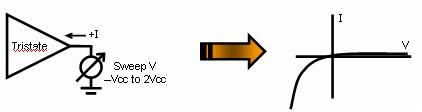

Ground clamp 曲线由来

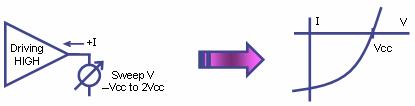

Pull up 曲线由来(此曲线需要考虑与clamp 曲线重复的部分)

Power clamp 曲线由来

注意:ibis 里面定义电流流入方向为正;在此图中pull up 以及power clamp 曲线都没经过转化(传说的vcc relative 没出现,^_^,使用Vcc relative 从目前得到的解释是模型可以应用在兼容电压模式,举个例子2.5v 兼容3.3V 的器件,2.5v 和3.3v 工作状态下可以使用相同的模型而不用建立两模型描述单个器件)

IBIS 模型在软件中的应用

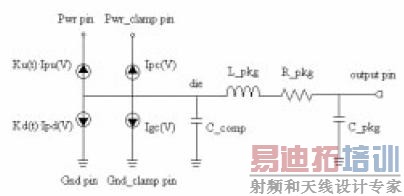

目前高速信号软件大部分都是spice-compatible 软件,而且很多都内嵌field solver分析传输线,因而在仿真中势必会把ibis 模型的信息转换成spice 信息来使用,来看看ibis 模型是如何转换成spice 信息使用的。看下如下的示意图, 当外接fixture,此部分电路可以直接在spice 中求解

当外接fixture,此部分电路可以直接在spice 中求解

但是VI 曲线仅仅描述的是DC 状态,那么在ibis 模型中描述瞬态的vt 曲线如何

转换值得商讨,看以下的等效图

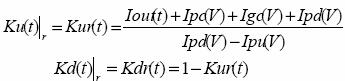

可以得出等式:-Iout=Ku*Ipu+Kd*Ipd+Ipc+Igc

如果rising/falling waveform 只有一条曲线,比如VCC+Rfixture,可假设![]()

得方程

如果有两条曲线,比如VCC/GND+Rfixture,Ku 与Kd 独立解出,从而可以得出仿真的瞬态曲线

比较有趣的问题

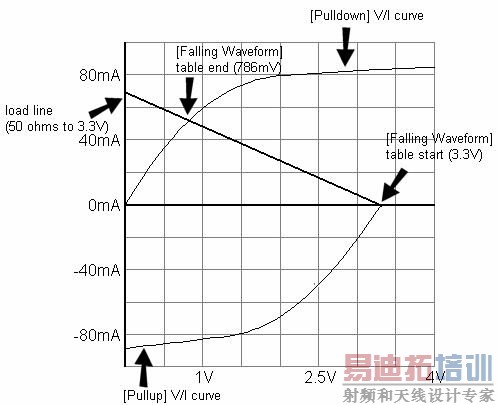

Vi/Vt 曲线的匹配(参考hyperlynx 的帮助)

对于falling waveform R_fixture=50 Ohms and V_fixture=3.3V负载线与pull up 曲线交界为falling waveform 起始点,与pull down 曲线交界为falling waveform 终点(始终记住pull up 是Vcc relative 需要转换)

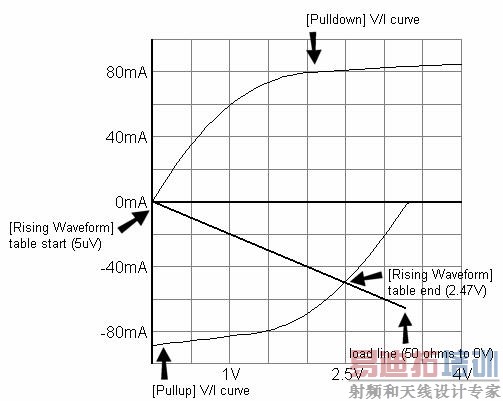

对于Rising waveform R_fixture=50 Ohms and V_fixture=3.3V

负载线与pull down 曲线交界为rising waveform 起始点,与pull up 曲线交界为rising waveform 终点

Package model 的应用

在ibis 里面有三个地方可以使用package model

A, [Pin] 语句里面,描述的是local package 参数,只有typ 值

B, [Pack]

语句里面,描述的是global package 参数,有slow/typ/fast 取值

C, [Define Package Model]里面,描述的是local package 参数,能带传输线,只有typ 值

Ramp 数值由来

测量vt 曲线

dv=(80%-20%)*(Vmaximum-Vminimum)

dt= t [80%*(Vmaximum-Vminimum)]- t [20%*(Vmaximum-Vminimum)]

总结

1,很多人告诉我说想验证ibis 模型,比较好玩,实际上你用软件检查后你会发现很少有其它事情我们可以做的。。。毕竟,你不是做芯片的,不要扁我!对于有问题的ibis 模型,我们有办法做什么事情么?没有,但你一定要知道问题在那儿,灭那些芯片的而不用被他们嘲笑,哈哈。

2,关于ibis 的发展前途,从目前发展趋势,它的归宿只有两个:

a 由于自动化的需要,迟早要成为一个编程语言,哈哈,又多一个求生的饭碗,大家快去学。。。

b 不要高兴太早,它有可能语法太庞大复杂最终被其它取代。。。

参考文献

1.Hyperlynx 帮助

2.The Development of Analog SPICE Behavioral Model Based on IBIS Model

3.Introduction to IBIS models and IBIS model making

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...