- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

Cadence 高速PCB的时序分析(2)

录入:edatop.com 点击:

列位看观,在上一次的连载中,我们介绍了什么是时序电路,时序分析的两种分类(同步和异步),并讲述了一些关于SDRAM 的基本概念。这一次的连载中,我们将介绍什么是定时问题,怎样保证接收端的建立和保持时间。

信号经过传输线到达接收端之后,必须满足建立时间和保持时间这两个时序参数,它们由接收器本身的特性决定,可以从芯片的数据手册中获得。时钟沿有效时,要求数据必须已经存在一段时间,这就是器件需要的建立时间(Setup Time);而时钟边沿触发之后,数据还必须要继续保持一段时间,以便能稳定的读取,这就是器件需要的保持时间(Hold Time)。数据信号在时钟沿触发前后持续的时间必须分别都要超过建立和保持时间,否则接收端可能不能正确地采样到数据,setup/hold 时间是时序问题产生的根源。

我们分析DSP 读取SDRAM 数据时怎样才能满足DSP 的建立和保持时间。不管列位看观在哪篇文献里看到了哪样的定时数学公式,请你将它遗忘。我们从来不需要死记硬背任何的数学公式,我们要的是聪明的分析头脑。

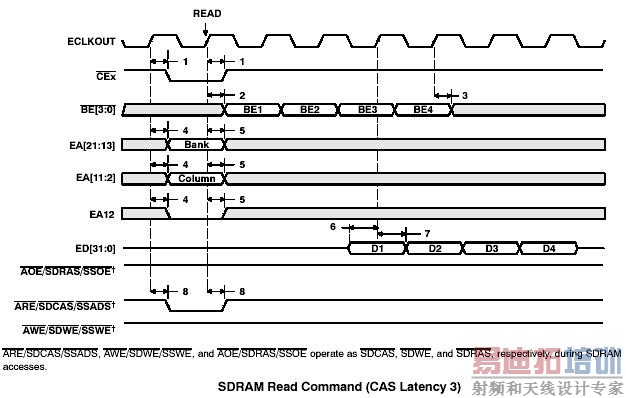

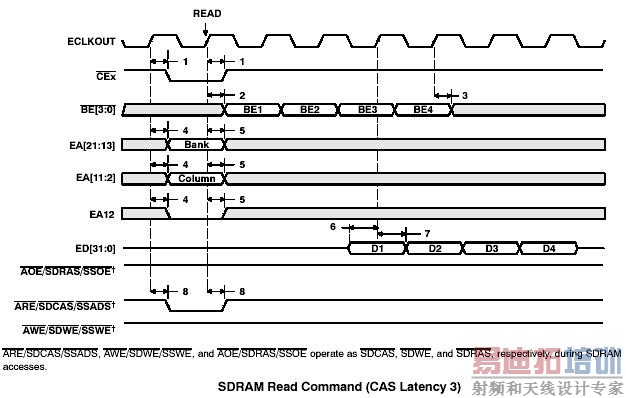

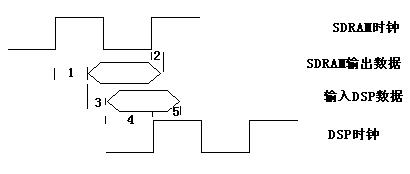

图6 为DSP 读取SDRAM 数据的定时,很明显,DSP 在ECLKOUT 的上升沿采样数据,图6 中的时间6 和时间7 分别是建立和保持时间,查TMS320C6713 数据手册获知建立时间最小为1.5ns,保持时间最小为2.5ns。

图6 TMS320C6713 读取SDRAM 数据的时序

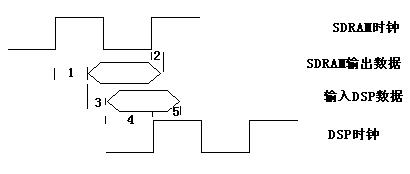

在DSP 读取SDRAM 数据时,SDRAM 在第一个时钟的上升沿后将数据放入总线,而DSP 总是在接下来的一个时钟上升沿触发时采样数据,如图7 所示,我们先假设SDRAM与DSP 的时钟是完全同步的。

显然欲满足DSP 的setup/hold,必须有:

T4 > DSP setup time;T5 > DSP hold time②

即Tclk-T1-T3 > DSP setup time; T2+T3 > DSP hold time

②请列位看观不要将此看做公式,我反对公式,赞成直观和推理。

图7 DSP 读取SDRAM 数据

很显然,我们弄明白了T1 、T2和T3的含义,就完全明白了setup/hold时间的需求!

什么是T1,直观而言,就是源端时钟上升沿有效到其在总线上放入的数据达到参考电平时的时间,这就是传说中的Tco。确定Tco的方法是在源端输出的末端直接相连一个测量负载,最常见的是50欧姆的电阻或者30pF的电容,然后测量负载上的信号电压达到一定电平的时间,这个电平称为测量电压(Vms),一般是信号高电平的一半。T3则是指在源端到第2个时钟周期上升沿后,数据还能准确地在数据线上保持多长时间(过了下文所说的First Switch Delay就不叫还在准确地保持)。很多文献中将T1和T3混为一谈,分别称为Tco-max和Tco-min,实际上是不准确的。

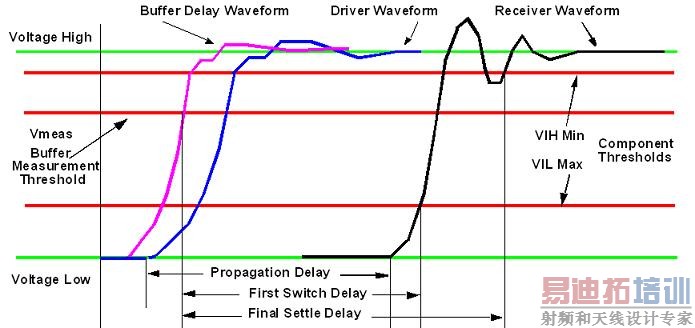

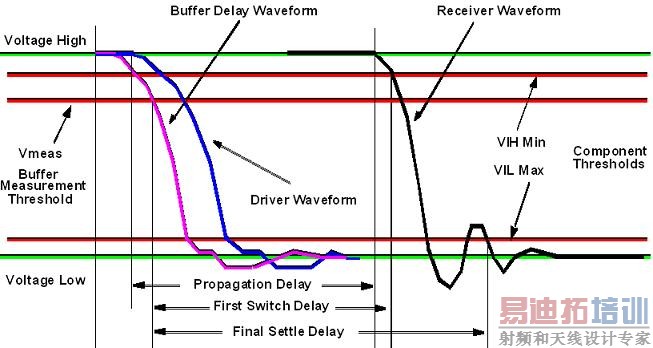

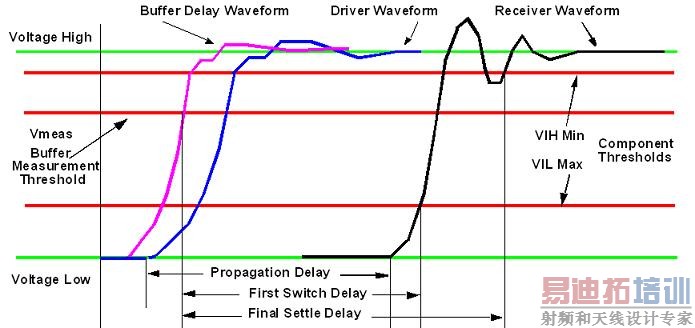

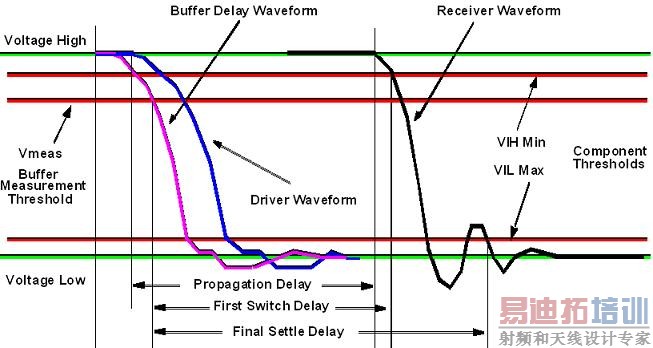

T3 是什么呢?列位看观一看就明白,不准确地说就是源端的数据到接收端数据之间的时间,那么这个时间具体是什么呢?就是传说中的飞行时间Tflight,注意Tflight 不同于传播时延,后者仅由传输线长和传输速度决定,而前者还受接收端负载大小的影响。Tflight 分为最小飞行时间Tflight-min 和最大飞行时间Tflight-max,在Cadence 软件中,Tflight-min 定义为First Switch Delay,Tflight-max 定义为Final Settle Delay,而这个定义,我认为,远远要超过飞行时间来得准确,让我们热情地歌颂它。如图8,假设数据从0 到1(上升沿),First Switch Delay指的是从这一刻起,接收端就不能准确地判断原来的0 了;而Final Settle Delay 这是指接收端只有从这一刻起才能准确地判断新来的1,虽然信号以前已经在1 上面跑过了一回(但是它又振荡回去了)。在数据的下降沿,如图9,看观们可以自己推理得出什么是First Switch Delay 和Final Settle Delay。很显然了,First Switch Delay 会被用在保持时间的计算中,而Final Settle Delay 则会用于建立时间的计算中。

图8 数据上升沿

图9 数据下降沿

于是乎,要满足Tclk-T1-T3 > DSP setup time 变成了要满足:

Tclk-Tco-max-Tflight-max > DSP setup time

而要满足T2+T3 > DSP hold time 就变成了要满足:

Tco-min+Tflight-min > DSP hold time

以上皆是基于SDRAM 的时钟与DSP 的时钟完全同步的假设,如果二者的时钟不同步,情况又当如何?我们假设SDRAM 的时钟比DSP 的早Tskew,很显然这个早(也就是DSP采样数据的晚)对于DSP 建立时间的获取是有利的(DSP 可以争取到更多的建立时间),而对保持时间是不利的。

有利就是说建立时间条件中的“>”更容易被满足,怎样才能更加容易满足,显然是将Tskew 加入方程左边,于是最终版的Tclk-Tco-max-Tflight-max > DSP setup time 应为

Tclk-Tco-max-Tflight-max+Tskew > DSP setup time

而保持时间中的“>”更难被满足,于是Tco-min+Tflight-min > DSP setup time 最终变成

Tco-min+Tflight-min -Tskew > DSP hold time

在本例的DSP 与SDRAM 互连中,SDRAM 的时钟由DSP 输出,SDRAM 时钟晚于DSP,于是本例应该满足的条件则是:

Tclk-Tco-max-Tflight-max -Tskew > DSP setup time

Tco-min+Tflight-min +Tskew > DSP hold time

经过一段痛苦的推理过程后,一切变得豁然开朗。请记住:在判断是该+还是该- Tskew时,请使用是否“有利于”等式成立法则!记得江core 提出过“三个有利于”,考研的时候被它搞晕了。

我们学会了这样的推理过程后,以后面对任何情况的CPU 与RAM 时序,都可以分析出来。表2 列出了TMS320C6713 和MT48LC4M32B2-7 的参数。

下面我们将要面对真实的Cadence 了,我们看看怎样仿真获得准确的Tflight-max 和Tflight-min。很抱歉,Cadence 中不计其数的设置搞得你我晕头转向,让我们无情地批判它。

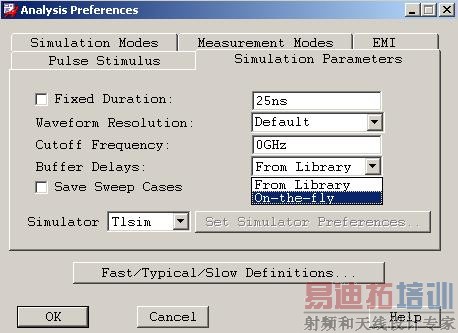

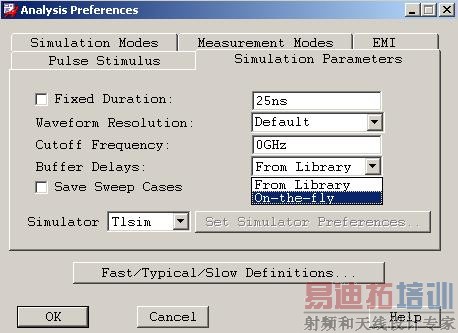

第一个设置:请在SigXplorer 中将Buffer Delay 设置为On-the-fly(图10),如果你有兴趣可以将Waveform Resolution 设置地更小,以便追求更大的仿真精度。Default 指的是周期的1/100。

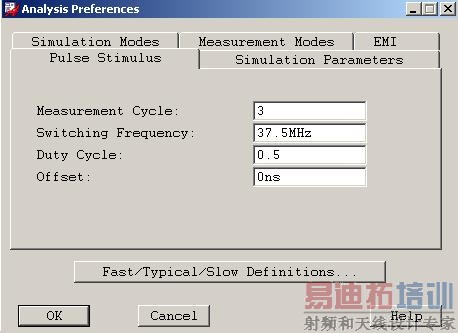

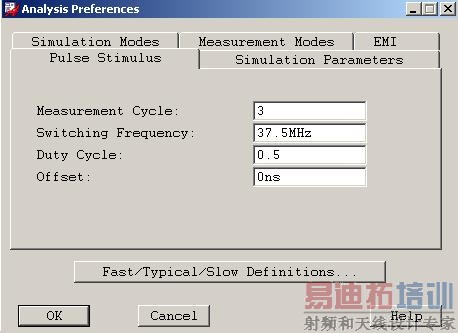

第二个设置:设置脉冲的Switching Frequency 为数据线的频率(也即时钟频率的一半,见图11)。

图10 设置Buffer Delay 为On-the-fly

图11 设置Switching Frequency 为数据线的频率

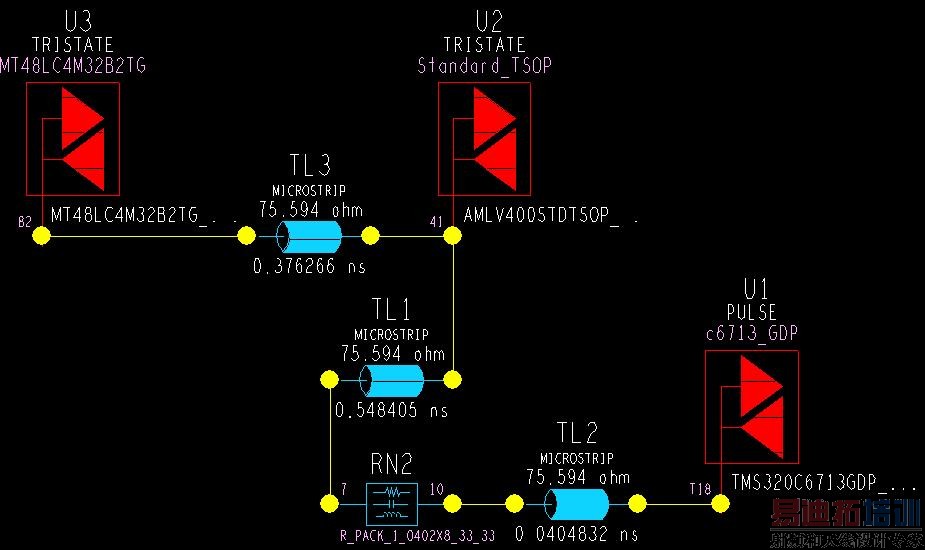

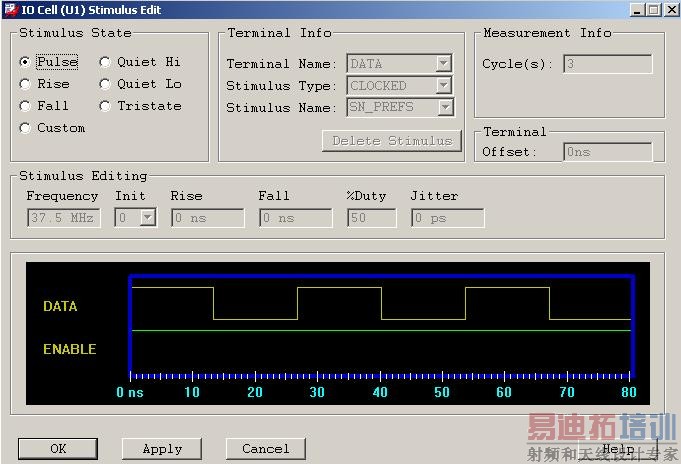

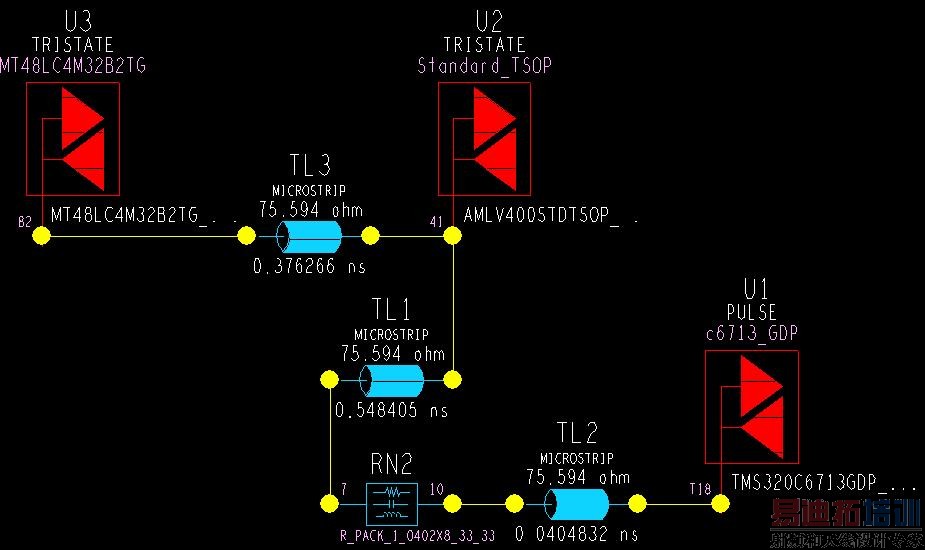

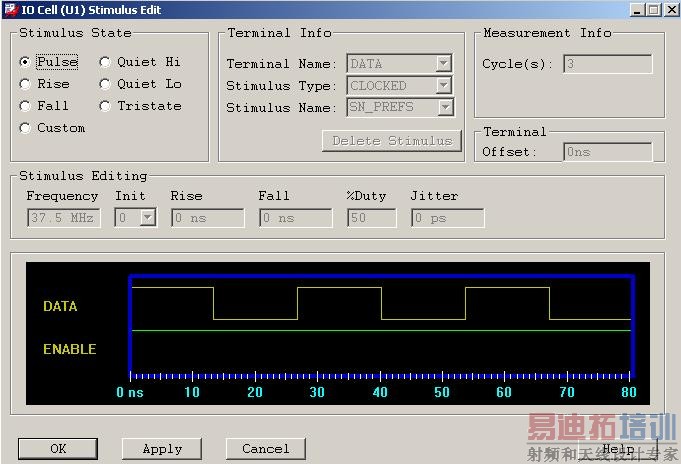

第三个设置:设置驱动端脉冲,如图13,在提取的如图12 的拓朴图中点击驱动端U1,在弹出的窗口中设置其为pulse。

图12 提取的拓朴

图13 设置驱动端脉冲

现在可以点击 开始仿真,得到了下面的仿真结果

开始仿真,得到了下面的仿真结果

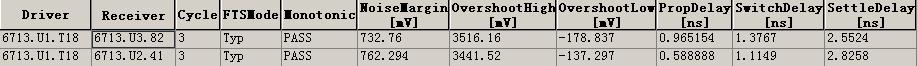

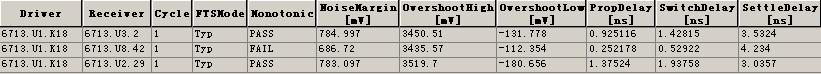

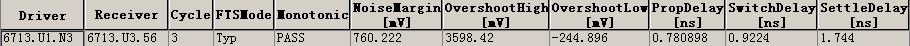

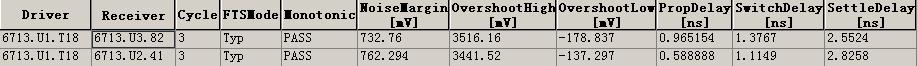

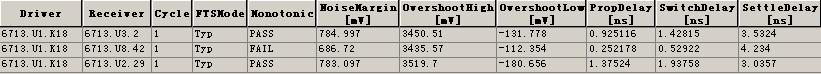

由于32 根数据线上的拓朴并非完全一样,我们将拓朴相同的归为一组BUS,共获得三组BUS 的Tflight-max 和Tflight-min 然后取所有中的最大和最小值。对另外两组数据BUS 执行同样的仿真后,获得的结论如下:

从三组结论中我们也看出这样一个事实,DSP 带越少的负载,Tflight-max 和Tflight-min 越接近于传播时延,这显然是合理的。

Tflight-min = 0.9224ns

Tflight-max = 3.5324ns

而时间偏移Tskew 则为0.8625ns,Tclk = 1/37.5mhz = 26.6667ns

Tclk-Tco-max-Tflight-max -Tskew =26.6667-3.5324-5.5-0.8625=16.7717ns

16.7717ns >1.5ns(DSP setup time)显然成立!

Tco-min+Tflight-min +Tskew =0.9224+2.5+0.8625=4.2849ns

4.2849ns >2.5ns(DSP hold time) 显然成立!

我们可以预测以当前的拓朴和负载情况,SDRAM 的数据频率跑到37.5mhz 是可以满足DSP 的定时要求的。上面两式好像满足的非常轻松,可以,事实上,我们给了Tclk 一个较大的值,既让数据运行在了较低的频率上。如果我们降低Tclk,相应的Tflight-max 则很可能会增加,要满足建立时间的难度要大一些。

我们惊讶地发现,欲保持时间似乎与工作频率无关!是的,事实正是如此!(我们不否认Tflight-min 会随着工作频率有微小的波动。)

另外,请记住:读写都要满足setup/hold!在DSP 写SDRAM 时,要满足SDRAM 的建立和保持时间!

让我们进入规则设置环节!规则,你如此可怕,以致于学习你需要费尽心机,肝肠寸断;规则,你如此可爱,以致于精通了你就可以在PCB 界潇洒地仗剑江湖,驰骋沙场;规则,你如此可恨,以致于不懂你,一切地原理图、PCB 绘制过程都是在重复地做着傻瓜的游戏。接下来,让我们践踏你,解剖你,玩死你。

(精彩内容,请听下回分解。列位看观,今天谈到这里先。)

连载待续 版权所有

21cnbao@21cn.com

宋宝华

2004-10-20

信号经过传输线到达接收端之后,必须满足建立时间和保持时间这两个时序参数,它们由接收器本身的特性决定,可以从芯片的数据手册中获得。时钟沿有效时,要求数据必须已经存在一段时间,这就是器件需要的建立时间(Setup Time);而时钟边沿触发之后,数据还必须要继续保持一段时间,以便能稳定的读取,这就是器件需要的保持时间(Hold Time)。数据信号在时钟沿触发前后持续的时间必须分别都要超过建立和保持时间,否则接收端可能不能正确地采样到数据,setup/hold 时间是时序问题产生的根源。

我们分析DSP 读取SDRAM 数据时怎样才能满足DSP 的建立和保持时间。不管列位看观在哪篇文献里看到了哪样的定时数学公式,请你将它遗忘。我们从来不需要死记硬背任何的数学公式,我们要的是聪明的分析头脑。

图6 为DSP 读取SDRAM 数据的定时,很明显,DSP 在ECLKOUT 的上升沿采样数据,图6 中的时间6 和时间7 分别是建立和保持时间,查TMS320C6713 数据手册获知建立时间最小为1.5ns,保持时间最小为2.5ns。

图6 TMS320C6713 读取SDRAM 数据的时序

在DSP 读取SDRAM 数据时,SDRAM 在第一个时钟的上升沿后将数据放入总线,而DSP 总是在接下来的一个时钟上升沿触发时采样数据,如图7 所示,我们先假设SDRAM与DSP 的时钟是完全同步的。

显然欲满足DSP 的setup/hold,必须有:

T4 > DSP setup time;T5 > DSP hold time②

即Tclk-T1-T3 > DSP setup time; T2+T3 > DSP hold time

②请列位看观不要将此看做公式,我反对公式,赞成直观和推理。

图7 DSP 读取SDRAM 数据

很显然,我们弄明白了T1 、T2和T3的含义,就完全明白了setup/hold时间的需求!

什么是T1,直观而言,就是源端时钟上升沿有效到其在总线上放入的数据达到参考电平时的时间,这就是传说中的Tco。确定Tco的方法是在源端输出的末端直接相连一个测量负载,最常见的是50欧姆的电阻或者30pF的电容,然后测量负载上的信号电压达到一定电平的时间,这个电平称为测量电压(Vms),一般是信号高电平的一半。T3则是指在源端到第2个时钟周期上升沿后,数据还能准确地在数据线上保持多长时间(过了下文所说的First Switch Delay就不叫还在准确地保持)。很多文献中将T1和T3混为一谈,分别称为Tco-max和Tco-min,实际上是不准确的。

T3 是什么呢?列位看观一看就明白,不准确地说就是源端的数据到接收端数据之间的时间,那么这个时间具体是什么呢?就是传说中的飞行时间Tflight,注意Tflight 不同于传播时延,后者仅由传输线长和传输速度决定,而前者还受接收端负载大小的影响。Tflight 分为最小飞行时间Tflight-min 和最大飞行时间Tflight-max,在Cadence 软件中,Tflight-min 定义为First Switch Delay,Tflight-max 定义为Final Settle Delay,而这个定义,我认为,远远要超过飞行时间来得准确,让我们热情地歌颂它。如图8,假设数据从0 到1(上升沿),First Switch Delay指的是从这一刻起,接收端就不能准确地判断原来的0 了;而Final Settle Delay 这是指接收端只有从这一刻起才能准确地判断新来的1,虽然信号以前已经在1 上面跑过了一回(但是它又振荡回去了)。在数据的下降沿,如图9,看观们可以自己推理得出什么是First Switch Delay 和Final Settle Delay。很显然了,First Switch Delay 会被用在保持时间的计算中,而Final Settle Delay 则会用于建立时间的计算中。

图8 数据上升沿

图9 数据下降沿

于是乎,要满足Tclk-T1-T3 > DSP setup time 变成了要满足:

Tclk-Tco-max-Tflight-max > DSP setup time

而要满足T2+T3 > DSP hold time 就变成了要满足:

Tco-min+Tflight-min > DSP hold time

以上皆是基于SDRAM 的时钟与DSP 的时钟完全同步的假设,如果二者的时钟不同步,情况又当如何?我们假设SDRAM 的时钟比DSP 的早Tskew,很显然这个早(也就是DSP采样数据的晚)对于DSP 建立时间的获取是有利的(DSP 可以争取到更多的建立时间),而对保持时间是不利的。

有利就是说建立时间条件中的“>”更容易被满足,怎样才能更加容易满足,显然是将Tskew 加入方程左边,于是最终版的Tclk-Tco-max-Tflight-max > DSP setup time 应为

Tclk-Tco-max-Tflight-max+Tskew > DSP setup time

而保持时间中的“>”更难被满足,于是Tco-min+Tflight-min > DSP setup time 最终变成

Tco-min+Tflight-min -Tskew > DSP hold time

在本例的DSP 与SDRAM 互连中,SDRAM 的时钟由DSP 输出,SDRAM 时钟晚于DSP,于是本例应该满足的条件则是:

Tclk-Tco-max-Tflight-max -Tskew > DSP setup time

Tco-min+Tflight-min +Tskew > DSP hold time

经过一段痛苦的推理过程后,一切变得豁然开朗。请记住:在判断是该+还是该- Tskew时,请使用是否“有利于”等式成立法则!记得江core 提出过“三个有利于”,考研的时候被它搞晕了。

我们学会了这样的推理过程后,以后面对任何情况的CPU 与RAM 时序,都可以分析出来。表2 列出了TMS320C6713 和MT48LC4M32B2-7 的参数。

| 参数 | 时间(ns) |

| MT48LC4M32B2 Tco-min | 2.5 |

| MT48LC4M32B2 Tco-max | 5.5 |

| TMS320C6713 setup time | 1.5 |

| TMS320C6713 hold time | 2.5 |

下面我们将要面对真实的Cadence 了,我们看看怎样仿真获得准确的Tflight-max 和Tflight-min。很抱歉,Cadence 中不计其数的设置搞得你我晕头转向,让我们无情地批判它。

第一个设置:请在SigXplorer 中将Buffer Delay 设置为On-the-fly(图10),如果你有兴趣可以将Waveform Resolution 设置地更小,以便追求更大的仿真精度。Default 指的是周期的1/100。

第二个设置:设置脉冲的Switching Frequency 为数据线的频率(也即时钟频率的一半,见图11)。

图10 设置Buffer Delay 为On-the-fly

图11 设置Switching Frequency 为数据线的频率

第三个设置:设置驱动端脉冲,如图13,在提取的如图12 的拓朴图中点击驱动端U1,在弹出的窗口中设置其为pulse。

图12 提取的拓朴

图13 设置驱动端脉冲

现在可以点击

由于32 根数据线上的拓朴并非完全一样,我们将拓朴相同的归为一组BUS,共获得三组BUS 的Tflight-max 和Tflight-min 然后取所有中的最大和最小值。对另外两组数据BUS 执行同样的仿真后,获得的结论如下:

从三组结论中我们也看出这样一个事实,DSP 带越少的负载,Tflight-max 和Tflight-min 越接近于传播时延,这显然是合理的。

Tflight-min = 0.9224ns

Tflight-max = 3.5324ns

而时间偏移Tskew 则为0.8625ns,Tclk = 1/37.5mhz = 26.6667ns

Tclk-Tco-max-Tflight-max -Tskew =26.6667-3.5324-5.5-0.8625=16.7717ns

16.7717ns >1.5ns(DSP setup time)显然成立!

Tco-min+Tflight-min +Tskew =0.9224+2.5+0.8625=4.2849ns

4.2849ns >2.5ns(DSP hold time) 显然成立!

我们可以预测以当前的拓朴和负载情况,SDRAM 的数据频率跑到37.5mhz 是可以满足DSP 的定时要求的。上面两式好像满足的非常轻松,可以,事实上,我们给了Tclk 一个较大的值,既让数据运行在了较低的频率上。如果我们降低Tclk,相应的Tflight-max 则很可能会增加,要满足建立时间的难度要大一些。

我们惊讶地发现,欲保持时间似乎与工作频率无关!是的,事实正是如此!(我们不否认Tflight-min 会随着工作频率有微小的波动。)

另外,请记住:读写都要满足setup/hold!在DSP 写SDRAM 时,要满足SDRAM 的建立和保持时间!

让我们进入规则设置环节!规则,你如此可怕,以致于学习你需要费尽心机,肝肠寸断;规则,你如此可爱,以致于精通了你就可以在PCB 界潇洒地仗剑江湖,驰骋沙场;规则,你如此可恨,以致于不懂你,一切地原理图、PCB 绘制过程都是在重复地做着傻瓜的游戏。接下来,让我们践踏你,解剖你,玩死你。

(精彩内容,请听下回分解。列位看观,今天谈到这里先。)

连载待续 版权所有

21cnbao@21cn.com

宋宝华

2004-10-20

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:基于PCB

仿真的高速时钟电路设计研究

下一篇:PCB载流能力计算

射频和天线工程师培训课程详情>>