- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

Cadence 高速PCB的时序分析(1)

1.引言

时序分析,也许是SI 分析中难度最大的一部分。我怀着满腔的期许给Cadence 的资深工程师发了一封e-mail,希望能够得到一份时序分析的案例,但是希望化作了泡影。资深工程师告诉我,他们还没有能够编写一个具体的案例。于是,我不得不将我的期许转化为自己研究并编写一个具体的案例,与广大PCB 工程师共享,令大彼天下PCB 寒士俱欢颜。既然有了共产主义的期许,自然就有了奋斗的信念。

如果你觉得好,请你顶一下;如果你觉得烂,请你顶起来骂一下。

2.从什么是时序电路谈起

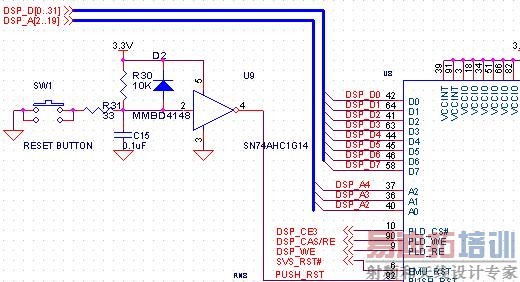

我的导师,一位诲人不倦的人类伟大灵魂工程师,当我将CPLD 连在了CPU 的数据、地址、读写和片选信号上,并企图在CPLD 中自定义几个寄存器使得这几个寄存器相对于CPU 就好似异步访问的存储空间时(如图1),他迷惘了。他认为我应该将CPU 的时钟输出到CPLD,不然就无法做到异步访问CPLD 的时序。

图1 CPLD 做异步访问存储器

原来这个世界从第一天起就将时序电路定义错了,它们定义为

y=f(x1,x2,…,xn,t1,t2,…,tn)

即函数值y 不仅与输入有关,还与时钟触发条件有关,正是因为时钟,才叫时序电路。

我要将这世界颠倒的黑都纠白了。为什么只有时钟能作触发条件,做触发条件的不一定只是时钟。图2 是TMS320C6713 这一DSP 的异步存储器读定时。很显然,在CPLD 中触发其将寄存器中数据放入总线的触发条件是读信号(图中画红线处触发)。这个读信号就成为二者之间的握手信号,在DSP 写CPLD 的时候握手信号则是写信号了。用CPLD 实现这个异步存储器的VHDL 程序如下:

re 定义为读信号输入,wr 定义为写信号输入,D_REG 定义为数据寄存器,data 是双向的数据总线

process(re)

BEGIN

if(cs='0' and re=’0’) then

data<=D_ REG;

end if;

…

END PROCESS;

process(wr)

BEGIN

if(cs='0' and wr=’0’) then

D_REG <= data;

end if;

…

END PROCESS;

图2 TMS320C6713 的异步存储器读定时

当然在上例中如果将DSP 的时钟输入接入CPLD,则可以更好的完成这个电路时序之间的匹配。如果不接入,也同样能通过编程改变DSP 的setup 和strobe 所占用的时钟周期数量来实现。

请记住:时钟本质上只是一个触发条件!跟其它的触发条件没有什么两样!

在CPU 访问SDRAM 时,握手信号即是时钟。于是乎,用Cadence 来做定时分析就分为两类:

1) 时钟握手信号――同步

2) 其它握手信号――异步

----------------------------------------------------------------------------------------------------------------------

请注意:此部分我的“时序电路”定义不严格,列位看观能明白我所言“触发”和“握手”之意既可。我仍然赞成我的导师将时钟接入CPLD。

3. 同步时序分析

列位看观,这个具体的案例将举的例子还是TMS320C6713,它将要访问MT48LC4M32B2这样一个SDRAM。首先介绍SDRAM的几个概念:

- CAS#等待时间(CL):指的是从CAS#信号有效开始要经过多少个时钟周期之后才能读取数据(写操作时数据与CAS#信号同时到达),通常可以选择2或者3;

- 突发长度(BL):SDRAM每次读写操作的数据量可以设定(也即支持突发式读写) ,可以是1、2、4、8 个字节或整页读写(一次读写一行数据),这样每次可以处理一批数据,从而提高了读写速度;

- 预充电(PRECHARGE):读写操作只对预充电过的行有效,所以每次读写操作前都要发出预充电指令或者在CAS#有效时,使A10为高①,即让SDRAM自动预充电;

- 自动刷新(REF):每隔一定的时间要向SDRAM发出一条刷新指令,这个时间可以通过读取SDRAM芯片的数据获得,通常为15.625μs;

- 自刷新(SELF):当对SDRAM暂时不进行操作,但又希望保留其内部数据时,可以发出自刷新信号,SDRAM 会自己刷新内部数据;

- 模式寄存器设置(MRS):通过一条指令对CL及BL进行设定。除了在初始化可以进行设置外,也可通过插入这条指令来改变CL或BL。

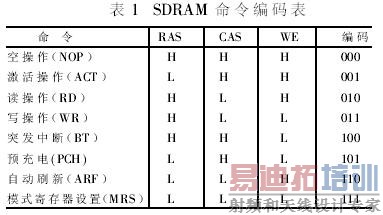

SDRAM的所有输入和输出都与系统时钟上升沿同步,并且由输入信号RAS、CAS、WE组合产生SDRAM控制命令,其基本的控制命令如表1所示。关于SDRAM 的操作有很多,如两个BANK的乒乓读写方式、突发式读写时的中断操作、低能耗方式的进入等等,我们可以在MT48LC4M32B2数据手册中看到各种操作时的时序图。

MT48LC4M32B2分为四个BANK,地址线的最高两位即为BANK的片选。其行地址为A0-A11,列地址为A0-A7,数据总线宽为32bit,需要在64ms内刷新4,096行。MT48LC4M32B2与TMS320C6713的连接如图,图中的CKE为SDRAM的时钟使能,被PULLUP。

(列位看观,今天谈到这里先。)

连载待续 版权所有

--------------------------------------------------------------------------------------

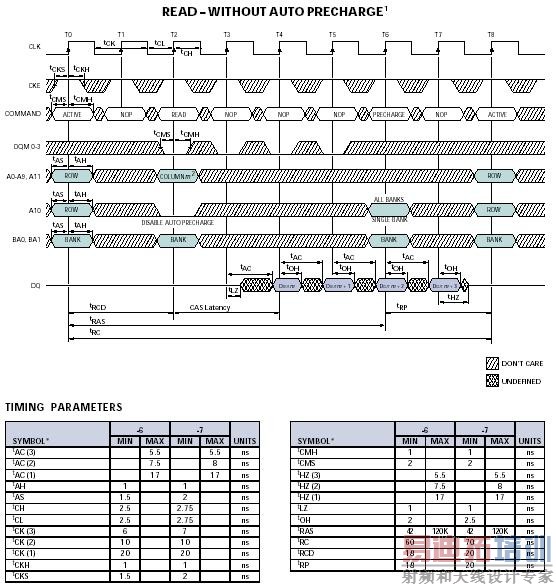

①图4和图5分别是自动预充电和无自动预充电时读SDRAM的时序,可以看出A10的不同。

图3 TMS320C6713与SDRAM

图4 自动预充电读时序

图5 无自动预充电读时序

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...