- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速电子线路的信号完整性设计(一)

1、引言

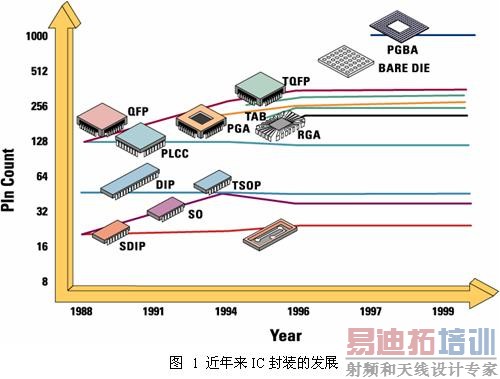

当今电子技术的发展日新月异,大规模超大规模集成电路越来越多地应用到通用系统中。同时,深亚微米工艺在IC设计中的使用,使得芯片的集成规模更大。从电子行业的发展来看,1992年只有40%的电子系统工作在30MHz以上的频率,而且器件多数使用DIP、PLCC等体积大、管脚少的封装形式,到1994年已有50%的设计达到了50MHz的频率,采用PGA,QFP,RGA等封装的器件越来越多。1996年之后,高速设计在整个电子设计领域所占的比例越来越大,100MHz以上的系统已随处可见,Bare Die,BGA,MCM这 些体积小、管脚数已达数百甚至上千的封装形式也已越来越多地应用到各类高速超高速电子系统中。图1所示为自80年代末IC封装的发展。

由上图可见,IC芯片的发展从封装形式来看,是芯片体积越来越小、引脚数越来越多。同时,由于近年来IC工艺的发展,使得其速度越来越高。由此可见,在当今快速发展的电子设计领域,由IC芯片构成的电子系统是朝着大规模、小体积、高速度的方向飞速发展的,而且发展速度越来越快。这样就带来了一个问题,即电子设计的体积减小导致电路的布局布线密度变大,而同时信号的频率还在提高,从而使得如何处理高速信号问题成为一个设计能否成功的关键因素。随着电子系统中逻辑和系统时钟频率的迅速提高和信号边沿不断变陡,印刷电路板的线迹互连和板层特性对系统电气性能的影响也越发重要。对于低频设计,线迹互连和板层的影响可以不考虑,当频率超过50MHz时,互连关系必须以传输线考虑,而在评定系统性能时也必须考虑印刷电路板板材的电参数。因此,高速系统的设计必须面对互连延迟引起的时序问题以及串扰、传输线效应等信号完整性问题。

2、高速电子设计的板级信号完整性

处理高速数字系统的振铃和串扰问题一直是一个令人头疼的问题,特别是在今天,越来越多的VLSI芯片工作在100MHz的频率以上,450MHz的CPU也将广泛应用,信号的边沿越来越陡(已达到ps级),这些高速器件性能的增加也给高速系统设计带来了困难。同时,高速系统的体积不断减小使得印制板的密度迅速提高。比较现在新的PC主板与几年前的主板,可以看到新的主板上加入了许多端接。信号完整性问题已经成为新一代高速产品设计中越来越值得注意的问题,这已是毋庸置疑的了。

信号完整性(Signal Integrity,简称SI)是指在信号线上的信号质量。差的信号完整性不是由某一单一 因素导致的,而是板级设计中多种因素共同引起的。主要的信号完整性问题包括反射、振铃、地弹、串扰等。

源端与负载端阻抗不匹配会引起线上反射,负载将一部分电压反射回源端。如果负载阻抗小于源阻抗,反射电压为负,反之,如果负载阻抗大于源阻抗,反射电压为正。布线的几何形状、不正确的线端接、经过连接器的传输及电源平面的不连续等因素的变化均会导致此类反射。

信号的振铃(ringing)和环绕振荡(rounding)由线上过度的电感和电容引起,振铃属于欠阻尼状态而环绕振荡属于过阻尼状态。信号完整性问题通常发生在周期信号中,如时钟等,振铃和环绕振荡同反射一样也是由多种因素引起的,振铃可以通过适当的端接予以减小,但是不可能完全消除。

在电路中有大的电流涌动时会引起地弹,如大量芯片的输出同时开启时,将有一个较大的瞬态电流在芯片与板的电源平面流过,芯片封装与电源平面的电感和电阻会引发电源噪声,这样会在真正的地平面(0V)上产生电压的波动和变化,这个噪声会影响其它元器件的动作。负载电容的增大、负载电阻的减小、地电感的增大、同时开关器件数目的增加均会导致地弹的增大。

振铃和地弹都属于信号完整性问题中单信号线的现象(伴有地平面回路),串扰则是由同一PCB板上的两条信号线与地平面引起的,故也称为三线系统。串扰是两条信号线之间的耦合,信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。

表1列出了高速电路中常见的信号完整性问题与可能引起该信号完整性的原因,并给出了相应的解决方案。

表 1 常见信号完整性(SI)问题及解决方法

| 表 1 常见信号完整性(SI)问题及解决方法 | |||

| 问题 | 可能原因 | 解决方法 | 变更的解决方法 |

| 过大的上冲 | 终端阻抗不匹配 | 终端端接 | 使用上升时间缓慢的驱动源 |

| 直流电压电平不好 | 线上负载过大 | 以交流负载替换直流负载 | 使用能提供更大驱动电流的驱动源 |

| 过大的串扰 | 线间耦合过大 | 使用上升时间缓 慢的主动驱动源 | 在被动接收端端接 , 重新布线或检查地平面 |

| 传播时间过长 | 传输线距离太长 , 没有开关动作 | 替换或重新布线 , 检查串行端接 | 使用阻抗匹配的驱动源 , 变更布线策略 |

在一个已有的PCB板上分析和发现信号完整性问题是一件非常困难的事情,即使找到了问题,在一个已成形的板上实施有效的解决办法也会花费大量时间和费用。那么,我们就期望能够在物理设计完成之前查找、发现并在电路设计过程中消除或减小信号完整性问题,这就是EDA工具需要完成的任务。先进的EDA信号完整性工具可以仿真实际物理设计中的各种参数,对电路中的信号完整性问题进行深入细致的分析。

新一代的EDA信号完整性工具主要包括布线前/布线后SI分析工具和系统级SI工具等。使用布线前SI分析工具可以根据设计对信号完整性与时序的要求在布线前帮助设计者选择元器件、调整元器件布局、规划系统时钟网络和确定关键线网的端接策略。SI分析与仿真工具不仅可以对一块PCB板的信号流进行分析,而且可以对同一系统内其它组成部分如背板、连接器、电缆及其接口进行分析,这就是系统级的SI分析工具。针对系统级评价的SI分析工具可以对多板、连接器、电缆等系统组成元件进行分析,并可通过设计建议来帮助设计者消除潜在的SI问题,它们一般都包括IBIS模型接口、2维传输线与串扰仿真、电路仿真、SI分析结果的图形显示等功能。这类工具可以在设计包含的多种领域如电气、EMC、热性能及机械性能等方面综合考虑这些因素对SI的影响及这些因素之间的相互影响,从而进行真正的系统级分析与验证。Mentor Graphics公司的ICX设计工具可以在时序与电气规则的驱动下进行TopDown式的布局及无网格布线,并提供多板分析功能,是典型的系统级SI工具。

3、理解和使用IBIS模型

如何在PCB板做板之前分析验证板级信号完整性(SI)问题,是设计成功的关键。这就需要用于SI分析的包含各种参数的准确模型。大多数SI分析工具都可将PCB板作为板材料和布线几何形状的函数进行分析计算,但是得到一个能够反映板上元件、连接器、电缆等器件的好的模型却相对较难,IBIS模型可以帮助设计者在存在SI约束的设计中获取准确的信息以进行分析和计算。

IBIS(Input/Output Buffer Information Specification)模型是一种基于V/I曲线的对I/O BUFFER快速准 确建模的方法,是反映芯片驱动和接收电气特性的一种国际标准,它提供一种标准的文件格式来记录如驱动源输出阻抗、上升/下降时间及输入负载等参数,非常适合做振铃和串扰等高频效应的计算与仿真。IBIS规范最初由一个被称为IBIS开放论坛的工业组织编写,这个组织是由一些EDA厂商、计算机制造商、半导体厂商和大学组成的。IBIS的版本发布情况为:1993年4月第一次推出Version1.0版,同年6月经修改后发布了Version1.1版,1994年6月在San Diego通过了Version2.0版,同年12月升级为Version2.1版,1995年12 月其Version2.1版成为ANSI/EIA-656标准,1997年6月发布了Version3.0版,同年9月被接纳为IEC 62012-1 标准,1998年升级为Version3.1版,1999年1月推出了当前最新的版本Version3.2版。

现在已有多家半导体器件生产厂家及CAE/EDA公司支持此IBIS规范,提供不同器件的IBIS模型及软件仿真工具,如Mentor Graphics公司既提供使用IBIS模型的仿真工具Interconnect Synthesis,同时提供Zeelan 的IBIS的仿真模型库,另外还可根据用户的特殊需求定制相应器件的IBIS模型。

IBIS本身只是一种文件格式,它说明在一标准的IBIS文件中如何记录一个芯片的驱动器和接收器的不同参数,但并不说明这些被记录的参数如何使用,这些参数需要由使用IBIS模型的仿真工具来读取。欲使用IBIS进行实际的仿真,需要先完成以下四件工作:

(1)获取有关芯片驱动器和接收器的原始信息源;

(2)获取一种将原始数据转换为IBIS格式的方法;

(3)提供用于仿真的可被计算机识别的布局布线信息;

(4)提供一种能够读取IBIS和布局布线格式并能够进行分析计算的软件工具。

IBIS是一种简单直观的文件格式,很适合用于类似于Spice(但不是Spice,因为IBIS文件格式不能直接被Spice工具读取)的电路仿真工具。它提供驱动器和接收器的行为描述,但不泄漏电路内部构造的知识产权细节。换句话说,销售商可以用IBIS模型来说明它们最新的门级设计工作,而不会给其竞争对手透露过多的产品信息。并且,因为IBIS是一个简单的模型,当做简单的带负载仿真时,比相应的全Spice三极管级模型仿真要节省10~15倍的计算量。

IBIS提供两条完整的V-I曲线分别代表驱动器为高电平和低电平状态,以及在确定的转换速度下状态转换的曲线。V-I曲线的作用在于为IBIS提供保护二极管、TTL图腾柱驱动源和射极跟随输出等非线性效应的建模能力。

由上可知,IBIS模型的优点可以概括为:

在I/O非线性方面能够提供准确的模型,同时考虑了封装的寄生参数与ESD结构;

提供比结构化的方法更快的仿真速度;

可用于系统板级或多板信号完整性分析仿真。可用IBIS模型分析的信号完整性问题包括:串扰、反 射、振铃、上冲、下冲、不匹配阻抗、传输线分析、拓扑结构分析。IBIS尤其能够对高速振铃和串扰进行准确精细的仿真,它可用于检测最坏情况的上升时间条件下的信号行为及一些用物理测试无法解决的情况;

模型可以免费从半导体厂商处获取,用户无需对模型付额外开销;

兼容工业界广泛的仿真平台。

当然,IBIS不是完美的,它也存在以下缺点:

许多芯片厂商缺乏对IBIS模型的支持。而缺乏IBIS模型,IBIS工具就无法工作。虽然IBIS文件可以 手工创建或通过Spice模型自动转换,但是如果无法从厂家得到最小上升时间参数,任何转换工具都无能为力;

IBIS不能理想地处理上升时间受控的驱动器类型的电路,特别是那些包含复杂反馈的电路;

IBIS缺乏对地弹噪声的建模能力。IBIS模型2.1版包含了描述不同管脚组合的互感,从这里可以提取 一些非常有用的地弹信息。它不工作的原因在于建模方式,当输出由高电平向低电平跳变时,大的地弹电压可以改变输出驱动器的行为。

伴随着大量的信号完整性问题的出现,IBIS已成为一种应用越来越广泛的器件仿真模型。许多公司、组织和大学开发了多种IBIS实用工具,主要的IBIS实用工具有:

IBISCHK,是IBIS模型的语法分析器,用来检查IBIS模型的语法错误;

S2iplt,此工具可以以图形方式显示IBIS模型的V/I曲线,它是属于UNIX版本的;

S2IBIS,此工具可以将现有的HSPICE、PSPICE或SPICE3模型转换为IBIS模型;

Visual IBIS Editor,是Hyperlynx公司开发的基于Windows平台的IBIS模型编辑、语法检查及V/I 曲线显示工具。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:PCB蛇形走线的作用

下一篇:Protel中有关PCB工艺的条目简介