- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

串扰理论试题

串扰理论试题

答卷人: 得分: 折合:

一.填空题:

前向串扰的大小取决于那些主要因素______________,后向串扰呢 _________________

两条平行线微带线A、B,如果正下方参考平面存在一与平行线垂直的沟壑,那么此时A线上上升阶段的跳变电压引起的对受侵害信号B的前后向串扰如何变化 (相对于理想的参考平面)_____________________________

为什么如此变化

答:

带状线中,共模平行线串扰和差模平行线串扰的大小关系如何

_______________________

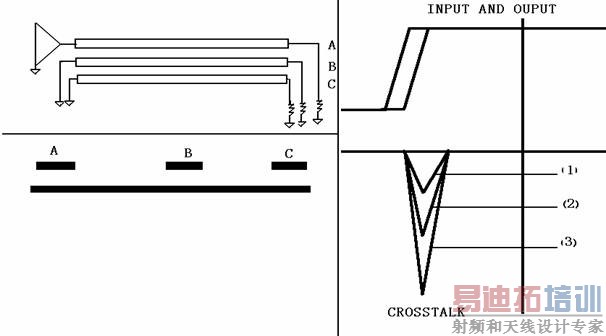

二. 图中为三根平行传输线A B C,右边有输入输出和串扰的幅值波形,试判断(1) (2) (3) 分别属于下面的那种情况.

(a) C 两端开路 ,A 对 B 的串扰.

(b) B 两端接地,A 对 C 的串扰.

(c) B 两端开路,A 对C 的串扰

______________________________________________________________________________

试分析一下两微带线平行线中干扰线的下降边缘对被干扰线引起串扰 (从感性,容性,前向,后向来分析 并且画出方向示意图)

三. 串扰是高速电路设计中必须考虑的一个问题,特别是对于相距很近的平行线中,在通常情况下,也可以从厂家提供的前向串扰系数(Kf)和后向串扰系数(Kb)得到具体大小的前后串扰值(Vf=Kf*L*Vm/Tr , Vb(tp>tr/2)=Kb*Vm ,Vb(tp<tr/2)=2Tpd*L*Vm/Tr*Kb)其中Vf 和 Vb 为串扰电压,Vm为干扰线最大电压 , L为串扰部分传输线长度)。下面是一工程师设计的电路走线图,按下面的要求,分析一下电路的串扰。

已知条件:

(1)传输线长度如图中所示。

(2)在t=0时刻,C端有一上升电压边缘(0 到 3.3)上升时间为2.5nsecs. 被干扰线处于1v的静态电压状态.

(3)Kb=0.170, Kf=0.0045, Tpd=175ps/in

(4)假设A端有很好的匹配

1)计算出A和D端的串扰电压.(写出详细步骤)

2)画出被干扰线的电压时间图.(前向串扰波形时间假设等于上升时间)

四. 下图为一平行线仿真图,其中一为0电压,一为2.5v下降边缘.分析下面的波形图并完成下列问题.

1) 请指出远端串扰和近端串扰各为那条线 _______________(A/B/C/D?)

2) 试分析为何C波形在干扰线没有电压跳变的情况下还环绕0v做振荡

__________________________________________________________________

3) 请详细列举能够减小串扰幅值和消除反复振荡的措施。

五. 我们知道,对于差分对走线,在大多数设计中都有等长、平行的要求,而且尽量能做到紧密耦合,但也有人提出异议,这样岂不是增加了互相之间的串扰,从而影响信号质量?你是怎样看待这个问题的?请详细分析,阐明你的观点。

| 答案.rar |

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...