- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

SI高速电路设计:高速PCB设计理论基础

第一部分信号完整性知识基础

第一章高速数字电路概述

现代的电子设计和芯片制造技术正在飞速发展,电子产品的复杂度、时钟和总线频率等等都呈快速上升趋势,但系统的电压却不断在减小,所有的这一切加上产品投放市场的时间要求给设计师带来了前所未有的巨大压力。要想保证产品的一次性成功就必须能预见设计中可能出现的各种问题,并及时给出合理的解决方案,对于高速的数字电路来说,最令人头大的莫过于如何确保瞬时跳变的数字信号通过较长的一段传输线,还能完整地被接收,并保证良好的电磁兼容性,这就是目前颇受关注的信号完整性(SI)问题。本章就是围绕信号完整性的问题,让大家对高速电路有个基本的认识,并介绍一些相关的基本概念。

1.1 何为高速电路

“高速电路”已经成为当今电子工程师们经常提及的一个名词,但究竟什么是高速电路

这的确是一个“熟悉”而又“模糊”的概念。而事实上,业界对高速电路并没有一个统一的定义,通常对高速电路的界定有以下多种看法:有人认为,如果数字逻辑电路的频率达到或者超过45MHZ-50MHZ,而且工作在这个频率之上的电路已经占到了整个电子系统一定的份量(比如说1/3),就称为高速电路;也有人认为高速电路和频率并没有什么大的联系,是否高速电路只取决于它们的上升时间;还有人认为高速电路就是我们早些年没有接触过,或者说能产生并且考虑到趋肤效应的电路;更多的人则对高速进行了量化的定义,即当电路中的数字信号在传输线上的延迟大于1/2上升时间时,就叫做高速电路,本文也沿用这个定义作为考虑高速问题的标准。

此外,还有一个容易产生混淆的是“高频电路”的概念,“高频”和“高速”有什么区别呢

对于高频,很多人的理解就是较高的信号频率,虽然不能说这种看法有误,但对于高速电子设计工程师来说,理解应当更为深刻,我们除了关心信号的固有频率,还应当考虑信号发射时同时伴随产生的高阶谐波的影响,一般我们使用下面这个公式来做定义信号的发射带宽,有时也称为EMI发射带宽:

F=1/(Tr*π),F是频率(GHz);Tr(纳秒)指信号的上升时间或下降时间。

通常当F>100MHz的时候,就可以称为高频电路。所以,在数字电路中,是否是高频电路,并不在于信号频率的高低,而主要是取决于上升沿和下降沿。根据这个公式可以推算,当上升时间小于3.185ns左右的时候,我们认为是高频电路。

对于大多数电子电路硬件设计工程师来说,完全没有必要拘泥于概念的差异,心中应该有个广义的“高速”定义,那就是:如果在确保正确的电气连接的前提下,电路仍不能稳定的高性能工作,而需要进行特殊的布局,布线,匹配,屏蔽等处理,那么,这就是“高速”设计。

1.2 高速带来的问题及设计流程剖析

虽然不少人对高速可能有了一点概念性的认识,但往往难以想象在所谓的“高速”情况下,会真正给实际的电路系统带来什么样的后果,这里我举几个实际的案例来剖析一下高速给PCB设计带来的一系列问题。

A.某公司早期开发的一个产品,一直工作良好,可是最近生产出来的一批却总是毛病不断,受到许多客户的抱怨。可是根本没有对设计进行任何变动,连使用的芯片也是同一型号的,原因是什么呢

B.某个PCB工程师Layout经验非常丰富,设计的产品很少出过问题,但最近设计了一块PCB板,却发现了EMC检测不合格的问题,改变布线也毫无效果,但以前类似的板子却没有这样的问题。

C.一个专业的内存模块设计工程师,从EDO内存到SDRAM的PC66,PC100,设计过很多项目,很少出现问题,可是自从内存时钟频率上到133MHz以上时,几乎很少有设计能一次性通过的。

简单分析一下上面的几个案例,A的情况是由于芯片的工艺改进造成的,虽然所使用的芯片基本电路功能一样,但随着的IC制造工艺水平的提高,信号的上升沿变快了,于是出现了反射、串扰等信号不完整的问题,从而导致突然失效;B例子中,通过细致地检测,最终发现是PCB板上有两个并排平行放置的电感元件,所以产生了较为严重的EMI;C中的内存设计师则是因为忽视了严格的拓补结构要求,在频率提高、时序要求更严格的情况下,非单调性和时钟偏移等问题造成了设计的内存模块无法启动。除了以上提到的三个实例,还有很多其他的问题,比如因为电容设计不当导致电源电压不稳而无法工作,数模接地不正确产生的干扰太严重使得系统不稳定等等。

随着电子技术的不断发展,类似于以上的各种问题层出不穷,而且可以预见,今后还会出现更多的这样或那样的问题。所以,了解信号完整性理论,进而指导和验证高速PCB的设计是一件刻不容缓的事情。

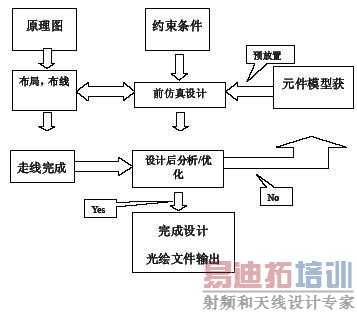

传统的PCB设计一般经过原理图设计、布局、布线、优化等四个主要步骤,由于缺乏高速分析和仿真指导,信号的质量无法得到保证,而且大部分问题必须等到制板测试后才能发现,这大大降低了设计的效率,提高了成本,显然在激烈的市场竞争下,这种设计方法是很不利的。于是,针对高速PCB设计,业界提出了一种新的设计思路,称为“自上而下”的设计方法,这是一种建立在实时仿真基础上优化的高效设计流程,见图1-1-1:

图1-1-1高速PCB设计流程

从上面的流程图可以看到,高速的PCB设计在完成之前,经过多方面的仿真、分析和优化,避免了绝大部分可能产生的问题,如果依托强大的EDA仿真工具,基本上能实现“设计即正确”目的。

在整个高速设计过程中,信号完整性工程师必须贯穿于设计的始终,Cadence公司的首席顾问Donald Telian曾给信号完整性工程师归纳了七点作用:

- 研究和定义(pioneering and defining)

- 分类和总结(Partitioning 和Approximating)

- 建模和测量(Modeling and Measuring)

- 设计和优化(Designing and optimizing)

- 量化和验证(Quantifying and verifying)

- 减少和简化(Reducing and simplifying)

- 联系和调试(Correlating and Debugging)

对于以上这七大作用的详细阐述,可以参见1997 high performance system Design Conference上Donald Telian的原稿。

1.3 相关的一些基本概念

在具体讨论信号完整性理论知识之前,这节中我们将对高速设计中经常提到的一些基本名词做些简单地整理和介绍,给初步接触高速的设计人员提供一个概念性的认识。

信号完整性(Signal Integrity):就是指电路系统中信号的质量,如果在要求的时间内,信号能不失真地从源端传送到接收端,我们就称该信号是完整的。

传输线(Transmission Line):由两个具有一定长度的导体组成回路的连接线,我们称之为传输线,有时也被称为延迟线。

集总电路(Lumped circuit):在一般的电路分析中,电路的所有参数,如阻抗、容抗、感抗都集中于空间的各个点上,各个元件上,各点之间的信号是瞬间传递的,这种理想化的电路模型称为集总电路。

分布式系统(Distributed System):实际的电路情况是各种参数分布于电路所在空间的各处,当这种分散性造成的信号延迟时间与信号本身的变化时间相比己不能忽略的时侯,整个信号通道是带有电阻、电容、电感的复杂网络,这就是一个典型的分布参数系统。

上升/下降时间(Rise/Fall Time):信号从低电平跳变为高电平所需要的时间,通常是量度上升/下降沿在10%-90%电压幅值之间的持续时间,记为Tr。

截止频率(Knee Frequency):这是表征数字电路中集中了大部分能量的频率范围(0.5/Tr),记为Fknee。,一般认为超过这个频率的能量对数字信号的传输没有任何影响。

特征阻抗(Characteristic Impedance):交流信号在传输线上传播中的每一步遇到不变的瞬间阻抗就被称为特征阻抗,也称为浪涌阻抗,记为Zo。可以通过传输线上输入电压对输入电流的比率值(V/I)来表示。

传输延迟(Propagation delay):指信号在传输线上的传播延时,与线长和信号传播速度有关,记为tpd

微带线(Micro-Strip):指只有一边存在参考平面的传输线。

带状线(Strip-Line):指两边都有参考平面的传输线。

趋肤效应(Skin effect):指当信号频率提高时,流动电荷会渐渐向传输线的边缘靠近,甚至中间将没有电流通过。与此类似的还有集束效应,现象是电流密集区域集中在导体的内侧。

反射(Reflection):指由于阻抗不匹配而造成的信号能量的不完全吸收,发射的程度可以有反射系数p表示。

过冲/下冲(Over shoot/under shoot):过冲就是指接收信号的第一个峰值或谷值超过设定电压——对于上升沿是指第一个峰值超过最高电压;对于下降沿是指第一个谷值超过最低电压,而下冲就是指第二个谷值或峰值。

振荡:在一个时钟周期中,反复的出现过冲和下冲,我们就称之为振荡。振荡根据表现形式可分为振铃(Ringing)和环绕振荡,振铃为欠阻尼振荡,而环绕振荡为过阻尼振荡。

匹配(Ternlination):指为了消除反射而通过添加电阻或电容器件来达到阻抗一致的效果。因为通常采用在源端或终端,所以也称为端接。

串扰:串扰是指当信号在传输线上传播时,因电磁耦合对相邻的传输线产生的不期望的电压噪声干扰,这种干扰是由于传输线之间的互感和互容引起的。

信号回流(Return current):指伴随信号传播的返回电流。

自屏蔽(Self shielding):信号在传输线上传播时,靠大电容耦合抑制电场,靠小电感耦合抑制磁场来维持低电抗的方法称为自屏蔽。

前向串扰(Forward Crosstalk):指干扰源对牺牲源的接收端产生的第一次干扰,也称为远端干扰(Far-end crosstalk)。

后向串扰(Forward Crosstalk):指干扰源对牺牲源的发送端产生的第一次干扰,也称为近端干扰(Near-end crosstalk)。

屏蔽效率(SE):是对屏蔽的适用性进行评估的一个参数,单位为分贝。

吸收损耗:吸收损耗是指电磁波穿过屏蔽罩的时候能量损耗的数量。

反射损耗:反射损耗是指由于屏蔽的内部反射导致的能量损耗的数量,他随着波阻和屏蔽阻抗的比率而变化。

校正因子:表示屏蔽效率下降的情况的参数,由于屏蔽物吸收效率不高,其内部的再反射会使穿过屏蔽层另一面的能量增加,所以校正因子是个负数,而且只使用于薄屏蔽罩中存在多个反射的情况分析。

差模EMI:传输线上电流从驱动端流到接收端的时候和它回流之间耦合产生的EMI,就叫做差模EMI。

共模EMI:当两条或者多条传输线以相同的相位和方向从驱动端输出到接收端的时候,就会产生共模辐射,既共模EMI。

发射带宽:即最高频率发射带宽,当数字集成电路从逻辑高低之间转换的时候,输出端产生的方波信号频率并不是导致EMI的唯一成分。该方波中包含频率范围更宽广的正弦谐波分量,这些正弦谐波分量是工程师所关心的EMI频率成分,而最高的EMI频率也称为EMI的发射带宽。

电磁环境:存在于给定场所的所有电磁现象的总和。

电磁骚扰:任何能引起装置、设备或系统性能降低或者对有生命或者无生命物质产生损害作用的电磁现象。

电磁干扰:电磁骚扰引起设备、传输通道和系统性能的下降。

电磁兼容性:设备或者系统在电磁环境中能正常工作且不对该环境中任何事物构成不能承受的电磁骚扰的能力。

系统内干扰:系统中出现由本系统内部电磁骚扰引起的电磁干扰。

系统间干扰:有其他系统产生的电磁干扰对一个系统造成的电磁干扰。

静电放电:具有不同静电电位的物体相互接近或者接触时候而引起的电荷转移。

建立时间(setup Time):建立时间就是接收器件需要数据提前于时钟沿稳定存在于输入端的时间。

保持时间(Hold Time):为了成功的锁存一个信号到接收端,器件必须要求数据信号在被时钟沿触发后继续保持一段时间,以确保数据被正确的操作。这个最小的时间就是我们说的保持时间。

飞行时间(Flight Time):指信号从驱动端传输到接收端,并达到一定的电平之间的延时,和传输延迟和上升时间有关。

Tco:是指器件的输入时钟边缘触发有效到输出信号有效的时间差,这是信号在器件内部的所有延迟总和,一般包括逻辑延迟和缓冲延迟。

缓冲延迟(buffer delay):指信号经过缓冲器达到有效的电压输出所需要的时间

时钟抖动(Jitter):时钟抖动是指时钟触发沿的随机误差,通常可以用两个或多个时钟周期差值来量度,这个误差是由时钟发生器内部产生的,和后期布线没有关系。

时钟偏移(Skew):是指由同样的时钟产生的多个子时钟信号之间的延时差异。

假时钟:假时钟是指时钟越过阈值(threshold)无意识地改变了状态(有时在VIL或VIH之间)。通常由于过分的下冲(undershoot)或串扰(crosstalk)引起。

电源完整性(Power Integrity): 指电路系统中的电源和地的质量。

同步开关噪声(Simultaneous Switch Noise):指当器件处于开关状态,产生瞬间变化的电流(di/dt),在经过回流途径上存在的电感时,形成交流压降,从而引起噪声,简称SSN。也称为△i噪声。

地弹(Ground Bounce):指由于封装电感而引起地平面的波动,造成芯片地和系统地不一致的现象。同样,如果是由于封装电感引起的芯片和系统电源差异,就称为电源反弹(Power Bounce)。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:特征阻抗介绍

下一篇:高速PCB设计中的一些问题