- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

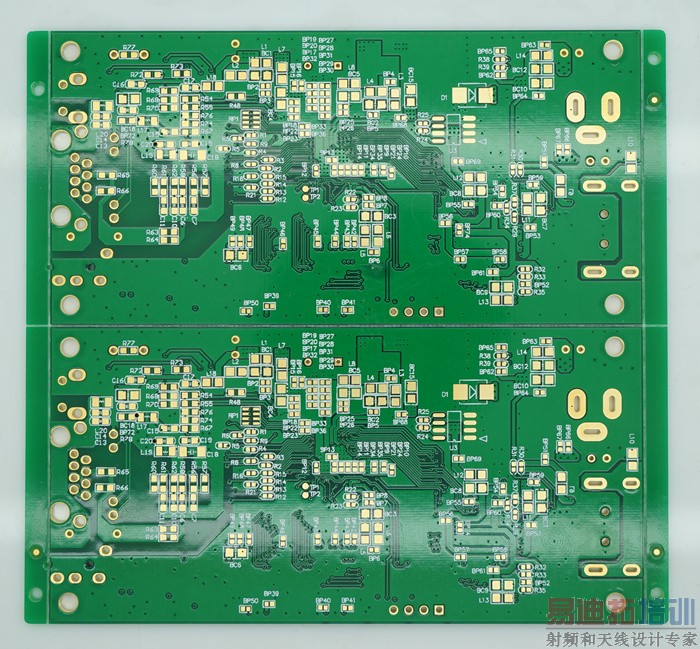

关于PCB高速差分信号的布线技巧

问:在 PCB设计 上靠近平行走高速差分信号线对的时候,在阻抗匹配的情况下,由于两线的相互耦合,会带来很多好处。但是有观点认为这样会增大信号的衰减,影响传输距离,为什么?我在一些地方的评估板上看到高速布线有的尽量靠近且平行,而有的却有意的使两线距离忽远忽近,哪一种效果会更好?我的信号1GHz以上,阻抗为50欧姆。在用软件计算时,差分线对也是以50欧姆来计算吗?还是以100欧姆来算?接收端差分线对之间可否加一匹配电阻?

答:会使高频信号能量衰减的原因一是导体本身的电阻特性(conductor loss),包括集肤效应(skin effect),另一是介电物质的dielectric loss。

这两种因子在电磁理论分析传输线效应(transmission line effect)时, 可看出他们对信号衰减的影响程度。差分线的耦合是会影响各自的特性阻抗, 变的较小,根据分压原理(voltage divider)这会使信号源送到线上的电压小一点。至于,因耦合而使信号衰减的理论分析我并没有看过,所以我无法评论。

对差分对的布线方式应该要适当的靠近且平行。所谓适当的靠近是因为这间距会影响到差分阻抗(differential impedance)的值,此值是设计差分对的重要参数。需要平行也是因为要保持差分阻抗的一致性。若两线忽远忽近,差分阻抗就会不一致,就会影响信号完整性(signal integrity)及时间延迟(timing delay)。差分阻抗的计算是 2(Z11 – Z12),其中,Z11是走线本身的特性阻抗,Z12是两条差分线间因为耦合而产生的阻抗,与线距有关。

所以,要设计差分阻抗为100欧姆时,走线本身的特性阻抗一定要稍大于50欧姆。至于要大多少,可用仿真软件算出来。接收端差分线对间的匹配电阻通常会加,其值应等于差分阻抗的值。

这样信号品质会好些。

易迪拓培训(edatop.com)(www.petpcb.com)有6年以上丰富的 PCB生产 、电子加工经验,是一家专业的一站式PCB供应商。 易迪拓培训(edatop.com) 在上海PCB生产、 线路板加工 等方面都有丰富经验,经过多年的发展,公司现已成为集“研发、生产、服务”为一体的专业化公司。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...