- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速FPGA设计电路板的要点(一)

电路板设计中,为了尽量减少串扰,微带线和带状线的布线可以遵循几种指导原则。对于双带线版图,布线是在两层内板上进行,两面都有一个电压参考面,这时最好所有邻近层板的导线都采用正交布线技术,尽量增大两个信号层之间的介质材料厚度,并最小化每个信号层与其邻近参考平面间的距离,同时保持所需要的阻抗。

微带线或带状线布线指导原则

线迹间距至少三倍于电路板布线层间介质层的厚度;最好使用仿真工具预先模拟其行为。

对临界高速网络用差分代替单端拓扑,以把共模噪声的影响减至最小。在设计限度内,尽量匹配差分信号路径的正负引脚。

减小单端信号的耦合效应,留有适当间隔(大于三倍的线迹宽度),或者是在不同板层上布线(邻近层布线彼此正交)。此外,使用仿真工具也是满足间距要求的一个好办法。

把信号端接信号间的并行长度减至最短。

同时转换噪声

时钟和I/O数据速率提高时,输出转换次数相应减少,信号路径放电充电期间的瞬态电流随之增大。这些电流可能造成板级接地弹跳现象,即接地电压/Vcc瞬间上升/下降。非理想电源的大瞬态电流会导致Vcc的瞬间下降(Vcc下降或凹陷)。下面给出了几条很好的板设计规则,有助于减少这些同时转换噪声的影响。

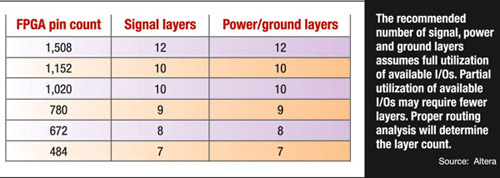

图为可用I/O被完全利用时推荐的信号、电源和接地层数目。

把不用的I/O引脚配置为输出引脚,并低电压驱动,以减小接地弹跳。

尽量减少同时转换输出引脚的数目,并使它们在整个FPGA I/O部分均匀分配。

不需要高边缘速率时,FPGA输出端选用低压摆率。

把Vcc安插到多层板的接地平面之间,以消除高速线迹对各层的影响。

把全部板层都用于Vcc和接地可使这些平面的电阻和电感最小,从而提供一个电容和噪声更低的低电感源,并在邻近这些平面的信号层上返回逻辑信号。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:高速FPGA设计电路板的要点(二)

下一篇:PCB钢网知识