- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

4片DDR PCB布线指南(上)

DDR布线通常是一款硬件产品设计中的一个重要的环节,也正是因为其重要性,网络上也有大把的人在探讨DDR布线规则,有很多同行故弄玄虚,把DDR布线说得很难,我在这里要反其道而行之,讲一讲DDR布线最简规则与过程。

如果不是特别说明,每个步骤中的方法同时适用于DDR1,DDR2和DDR3。PCB设计软件以Cadence Allgro 16.3为例。

第一步,确定拓补结构(仅在多片DDR芯片时有用)

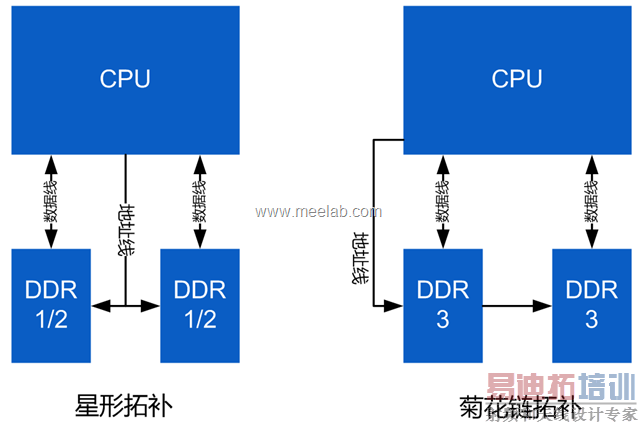

首先要确定DDR的拓补结构,一句话,DDR1/2采用星形结构,DDR3采用菊花链结构。拓补结构只影响地址线的走线方式,不影响数据线。以下是示意图。

星形拓补就是地址线走到两片DDR中间再向两片DDR分别走线,菊花链就是用地址线把两片DDR“串起来”,就像羊肉串,每个DDR都是羊肉串上的一块肉,哈哈,开个玩笑。

第二步,元器件摆放

确定了DDR的拓补结构,就可以进行元器件的摆放,有以下几个原则需要遵守:

原则一,考虑拓补结构,仔细查看CPU地址线的位置,使得地址线有利于相应的拓补结构

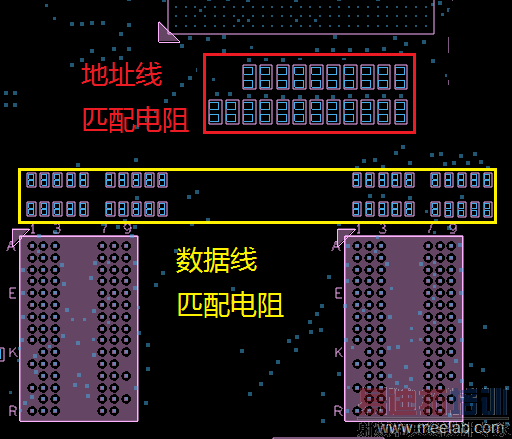

原则二,地址线上的匹配电阻靠近CPU

原则三,数据线上的匹配电阻靠近DDR

原则四,将DDR芯片摆放并旋转,使得DDR数据线尽量短,也就是,DDR芯片的数据引脚靠近CPU

原则五,如果有VTT端接电阻,将其摆放在地址线可以走到的最远的位置。一般来说,DDR2不需要VTT端接电阻,只有少数CPU需要;DDR3都需要VTT端接电阻。

原则六,DDR芯片的去耦电容放在靠近DDR芯片相应的引脚

以下是DDR2的元器件摆放示意图(未包括去耦电容),可以很容易看出,地址线可以走到两颗芯片中间然后向两边分,很容易实现星形拓补,同时,数据线会很短。

以下是带有VTT端接电阻的DDR2元器件摆放示意图,在这个例子中,没有串联匹配电阻,VTT端接电阻摆放在了地址线可以到达的最远距离。

以下是DDR3元器件摆放示意图,请注意,这里使用的CPU支持双通道DDR3,所以看到有四片(参考设计是8片)DDR3,其实是每两个组成一个通道,地址线沿着图中绿色的走线传递,实现了菊花链拓补。地址线上的VTT端接电阻摆放在了地址线可以到达的最远的地方。同样地,数据线上的端接电阻也放置在了靠近DDR3芯片的位置,数据线到达CPU的距离很短。同时,可以看到,去耦电容放置在了很靠近DDR3相应电源引脚的地方。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:数字电路PCB设计技巧(下)

下一篇:电路板设计-磁珠的作用和选用