- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

PCB设计减小串扰的一般规则

录入:edatop.com 点击:

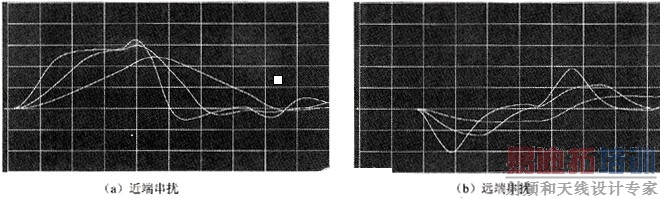

信号上升时间短是高速信号的一个重要特征,它对信号完整性的影响很大。那么保持系统本身参数不变,改变输入信号的上升时间,如图所示分别为上升时间0.5 ns、1 ns和2 ns时的近端及远端串扰波形。

图 信号上升时间不同时的近端和远端串扰

由图所示可见,上升沿的串扰的影响相当大,随着上升时间的变短,特别是当平行走线长度小于饱和长度时,串扰电压幅度将迅速减小。在现代高速设计中,具有快速边沿速率的器件越来越被广泛使用,这个问题必须引起注意。

从上面的分析中可以得到一些减小串扰的一般规则:

· 在满足系统设计要求的情况下,尽量使用边沿速率较慢的器件,因为它对串扰的影响最大;

· 加大布线间距,减小平行走线长度;

· 在设计目标阻抗时,应该尽量使导体靠近参考平面即减小介质层厚度,这样传输线可以紧密地与参考平面耦合,从而减小对邻近信号线的干扰;

· 如果有可能,信号线应该设计成带状线或埋式微带线,以获得较好的串扰抑制效果;

· 相邻信号层的走线应彼此正交,以减小耦合:

· 对于要求十分严格的系统可以使用差分走线,如系统时钟:

· 正确的端接可以减小或消除反射,从而减小串扰;

· 如果布线空间允许,可以在串扰严重的两条线之间插入一条地线以降低耦合,并减小串扰;

· 妥善布局,防止布线时出现拥挤。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:4片DDR

PCB布线指南(中)

下一篇:数字电路PCB设计技巧(下)

射频和天线工程师培训课程详情>>