- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

4片DDR PCB布线指南(下)

第四步,设置线宽与线距

1. DDR走线线宽与阻抗控制密切相关,经常可以看到很多同行做阻抗控制。对于纯数字电路,完全有条件针对高速线做单端阻抗控制;但对于混合电路,包含高速数字电路与射频电路,射频电路比数字电路要重要的多,必须对射频信号做50欧姆阻抗控制,同时射频走线不可能太细,否则会引起较大的损耗,所以在混合电路中,本人往往舍弃数字电路的阻抗控制。到目前为止,本人设计的混合电路产品中,最高规格的DDR是DDR2-800,未作阻抗控制,工作一切正常。

2. DDR的供电走线,建议8mil以上,在Allegro可以针对一类线进行物理参数的同意设定,我本人喜欢建立PWR-10MIL的约束条件,并为所有电源网络分配这一约束条件。

3. 线距部分主要考虑两方面,一是线-线间距,建议采用2W原则,即线间距是2倍线宽,3W很难满足;二是线-Shape间距,同样建议采用2W原则。对于线间距,也可以在Allegro中建立一种约束条件,为所有DDR走线(XNET)分配这样的约束条件。

4. 还有一种可能需要的规则,就是区域规则。Allegro中默认的线宽线距都是5mil,在CPU引脚比较密集的时候,这样的规则是无法满足的,这就需要在CPU或DDR芯片周围设定允许小间距,小线宽的区域规则。

第五步,走线

走线就需要注意的内容比较多,这里只做少许说明。

所有走线尽量短

走线不能有锐角

尽量少打过孔

保证所有走线有完整的参考面,地平面或这电源平面都可以,对于交变信号,地与电源平面是等电位的

尽量避免过孔将参考面打破,不过这在实际中很难做到

走完地址线和数据后,务必将DDR芯片的电源脚,接地脚,去耦电容的电源脚,接地脚全部走完,否则在后面绕等长时会很麻烦的

第六步,设置等长规则

对于数据线,DDR1/2与DDR3的规则是一致的:每个BYTE与各自的DQS,DQM等长,即DQ0:7与DQS0,DQM。等长,DQ8:15与DQS1,DQM1等长,以此类推。

地址线方面的等长,要特别注意,DDR1/2与DDR是很不一样的。

对于DDR1/2,需要设定每条地址到达同一片DDR的距离保持等长。

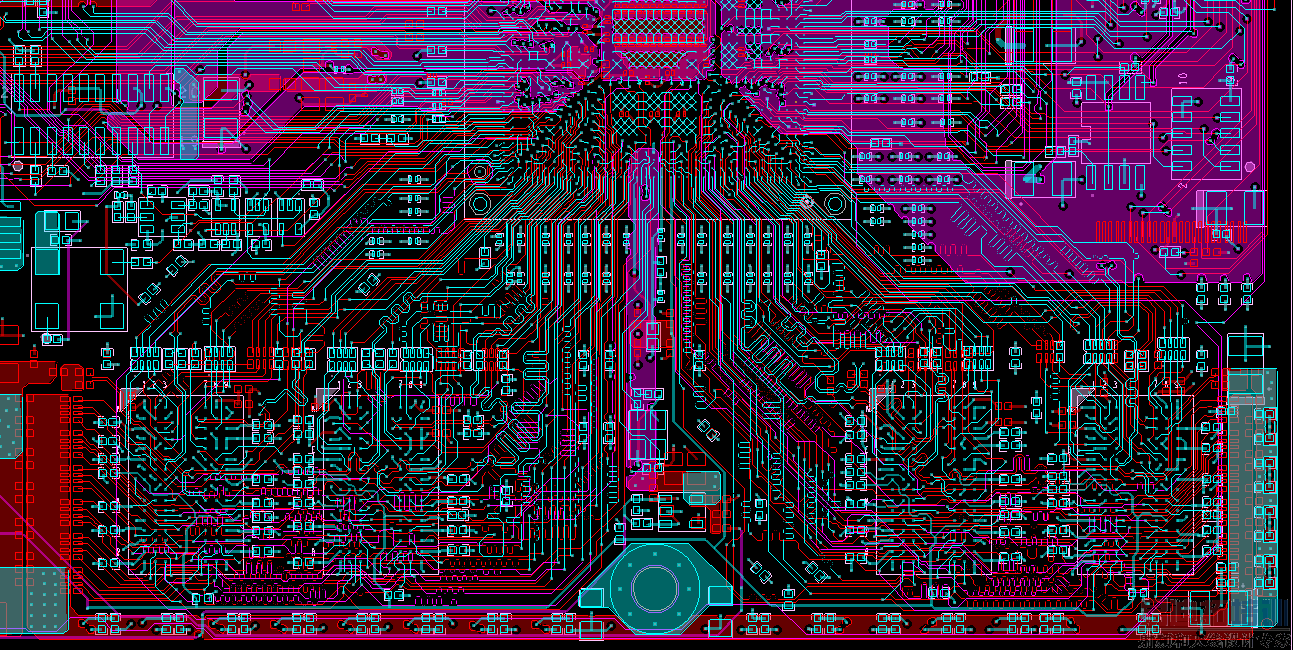

对于DDR3,地址线的等长往往需要过孔来配合,具体的规则均绑定在过孔上和VTT端接电阻上,如下图。可以看到,CPU的地址线到达过孔的距离等长,过孔到达VTT端接电阻的距离也等长。

补充一点,很多时候,地址线的等长要求不严格,这一点我还没有尝试过。在本人设计的这些产品中,地址线,数据线都做了25mil的Relative Propagation Delay的等长规则设定。关于等长规则设定的细节在这里不再赘述。

第七步,绕等长

完成等长规则的设定后,最后一步也是工作量最大的一步:绕等长。

在这一步,我认为只有一点规则需要注意:尽量采用3倍线宽,45度角绕等长。

绕等长完成后,最好把DDR相关网络锁定,以免误动。

到这里,DDR走线就已经完成了,在本人设计过的三,四十种产品中,都是按照上面的规则与过程完成的,DDR2最高规格是DDR2-800,512MB,DDR3最高规格是DDR3-1600,1GB,都可以很稳定的工作,无论性能还是可靠性,都未曾出过问题。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:Iphone6手机EMC设计简析(上)

下一篇:超薄智能手机PCB设计探讨(上)