- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

PCB设计布线对信号延迟的影响分析(一)

信号在媒质中传播时,其传播速度受信号载体以及周围媒质属性决定。在PCB(印刷电路板)中信号的传输速度就与板材DK(介电常数),信号模式,信号线与信号线间耦合以及绕线方式等有关。随着PCB走线信号速率越来越高,对时序要求较高的源同步信号的时序裕量越来越少,因此在PCB设计阶段准确知道PCB走线对信号时延的影响变的尤为重要。本文基于仿真分析DK,串扰,过孔,蛇形绕线等因素对信号时延的影响。

1.引言

信号要能正常工作都必须满足一定的时序要求,随着信号速率升高,数字信号的发展经历了从共同步时钟到源同步时钟以及串行(serdes)信号。在当今的消费类电子,通信服务器等行业,源同步和串行信号占据了很大的比重。串行信号比如常见PCIE,SAS,SATA,QPI,SFP+,XUAI,10GBASE-KR等信号,源同步信号比如DDR信号。

串行信号在发送端将数据信号和时钟(CLK)信号通过编码方式一起发送,在接收端通过时钟数据恢复(CDR)得到数据信号和时钟信号。由于时钟数据在同一个通道传播,串行信号对和对之间在PCB上传输延时要求较低,主要依靠锁相环(PLL)和芯片的时钟数据恢复功能。

源同步时钟主要是DDR信号,在DDR设计中,DQ(数据)信号参考DQS(数据选通)信号,CMD(命令)信号和CTL(控制)信号参考CLK(时钟)信号,由于DQ的速率是CMD DDR2/ DDR3.DDR4预计在2015年将成为消费类电子的主要设计,随着DDR信号速率的不断提高,在DDR4设计中特别是DQ和DQS之间传输时延对设计者提出更高的挑战。

在PCB设计的时候为了时序的要求需要对源同步信号做一些等长,一些设计工程师忽略了这个信号等长其实是一个时延等长,或者说是一个‘时间等长’。

2.传输时延简介

Time delay又叫时延(TD),通常是指电磁信号或者光信号通过整个传输介质所用的时间。在传输线上的时延就是指信号通过整个传输线所用的时间。

Propagation delay又叫传播延迟(PD),通常是指电磁信号或者光信号在单位长度的传输介质中传输的时间延迟,与“传播速度”成反比例(倒数)关系,单位为“Ps/inch”或“s/m”。

从定义中可以看出时延=传播延迟*传输长度(L)

其中v为传播速度,单位为inch/ps或m/s c为真空中的光速(3X108 m/s)

εr为介电常数PD为传播延迟,单位为Ps/inch或s/m TD为信号通过长度为L的传输线所产生的时延L为传输线长度,单位为inch或m

从上面公式可以知道,传播延迟主要取决于介质材料的介电常数,而传播时延取决于介质材料的介电常数、传输线长度和传输线横截面的几何结构(几何结构决定电场分布,电场分布决定有效介电常数)。严格来说,不管是延迟还是时延都取决于导体周围的有效介电常数。在微带线中,有效介电常数受横截面的几何结构影响比较大;而串扰,其有效介电常数受奇偶模式的影响较大;不同绕线方式有效介电常数受其绕线方式的影响。

3.仿真分析过程

3.1微带线和带状线传输时延

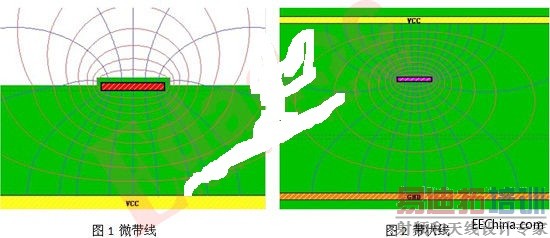

PCB中微带线是指走线只有一个参考面,如下图1;带状线是指走线有2个参考面,如下图2。

带状线由于电磁场都被束缚在两个参考面之间的板材中,所以走线的有效介电常数为板材的介电常数。

微带线会导致部分电磁场暴露在空气中,空气的相对介电常数约为1.0006,板材如常规FR4的介电常数为4.2,那么微带线的有效介电常数在1和4.2之间,可以利用下面的公式计算微带线的有效介电常数「Collins,1992」:

εe = (εr +1)/2 + (εr -1)/2(1+12H/W)-1/2 + F -0.217(εr -1)T/√WH 3.1 F = 0.02 (εr -1)(1-W/H)2 (W/H 1) 3.2

其中,εe为有效介电常数,εr为电路板材料的介电常数,H为导线高于地平面的高度,W为导线宽度,T为导线厚度。

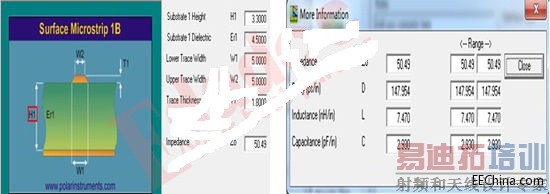

图4微带线层叠与时延

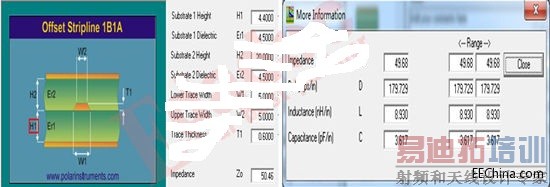

图5带状线层叠和时延

在图4和图5的层叠结构下,1000mil的走线时延差=179.729ps-147.954ps=31.775ps,可以看出这个差距是非常大的。在做源同步的DDR同组等长时候只考虑物理等长会带来很严重的''时间不等长。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:电源完整性(PI)仿真简介

下一篇:软板常见结构问题