- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

PCB设计布线对信号延迟的影响分析(二)

3.2走线和过孔传输时延

在PCB设计时候,经常会遇到走线换层,走线换层必须借助于过孔。但长度相等的过孔和走线之间的时延并不相等。过孔的时延可以用式3.3表示

TD_via=√LC 3.3

其中TD_via表示信号经过过孔的时延,L表示过孔的寄生电感,C表示过孔的寄生电容。从式3.3可以看出寄生电容和寄生电感都会导致过孔的传输时延变大。而不同过孔结构寄生参数也会发生改变。下面通过仿真分析过孔时延和传输线时延时间的偏差。

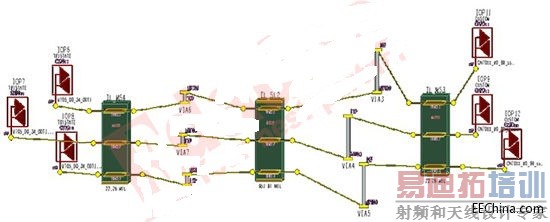

图6过孔结构及寄生参数

如图6所示过孔结构时延可以根据式3.3计算出:

TD_via=√LC=sqr(0.4021pf*1326.2pH)=23.1ps式3.4

由式3.4可以看出,结构如图6所示过孔的传输时延为23.1ps.而对于普通FR4板材的微带线,1.6mm走线传输时延约为11ps,对于带状线约为12.5ps.通过计算可以看出相同长度的走线和过孔之间的时延相差是非常大的。因此对设计工程师来讲设计的时候尽量做到以下两点:

1)需要做等长的信号要尽量走同层,换层时需要注意总的长度要保持相等并且每层走线都需要等长。

2)需要等长的信号走相同走线层可以保持过孔的时延一致,从而消除过孔时延不一致带来的影响。

3.3串扰对信号时延的影响。

PCB板上线与线的间距很近,走线上的信号可以通过空间耦合到其相邻的一些传输线上去,这个过程就叫串扰。串扰不仅可以影响到受害线上的电压幅值,同时还会影响到受害线上信号的传输时延。

图7串扰拓扑图

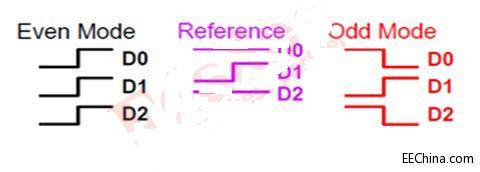

如图7串扰拓扑图所示,假设有3根相互耦合的传输线,中间的一根线(图8中D1)为受害线,两边的线(图8中D0)

1,假设两边的攻击线中没有信号,即不存在串扰,此种情况作为参考基准线(Reference);2,假设攻击线和受害线切换状态一致,此种情况为偶模(Even Mode)

3,假设攻击线和受害线切换状态相反,此种情况为奇模(Odd Mode)

图8串扰仿真中激励

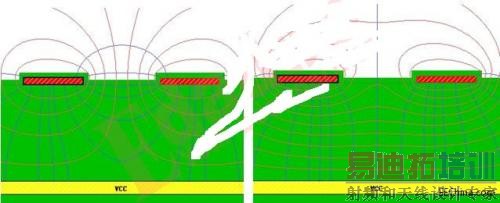

奇偶模式空间电磁场分布(如图9)

图9奇模电磁场分布图10偶模电磁场分布

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:PCB设计高可靠性特征(一)

下一篇:电源完整性(PI)仿真简介