- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速PCB设计中信号完整性分析(一)

摘要:

由于系统时钟频率和上升时间的增长,信号完整性设计变得越来越重要。不幸的是,绝大多数数字电路设计者并没意识到信号完整性问题的重要性, 或者是直到设计的最后阶段才初步认识到。

本篇介绍了高速数字硬件电路设计中信号完整性在通常设计的影响。 这包括特征阻抗控制、终端匹配、电源和地平面、信号布线和串扰等问题。掌握这些知识,对一个数字电路设计者而言,可以在电路设计的早期,就注意到潜在可能的信号完整性问题,还可以帮助设计则在设计中尽量避免信号完整性对设计性能的影响。

尽管,信号完整性一直以来都是硬件工程师必备的设计经验中的一项,但是在数字电路设计中长期被忽略。在低速逻辑电路设计时代,由于信号完整性相关的问题很少出现,因此对信号完整性的考虑本认为是浪费效率。然而近几年随着时钟率和上升时间的增长,信号完整性分析的必要性和设计也在增长。不幸的是,大多数设计者并没有注意到,而仍然在设计中很少去考虑信号完整性的问题。

现代数字电路可以高达 GHz 频率并且上升时间在 50ps 以内。在这样的速率下,在 PCB设计走线上的疏忽即使是一个英尺,而由此造成的电压、时延和接口问题将不仅仅局限在这一根线上,还将会影响的全板及相邻的板。

这个问题在混合电路中尤为严重。例如,考虑到在一个系统中有高性能的 ADC 到数字化接收模拟信号。散布在 ADC 器件的数字输出端口上的能量可能很容易就达到 130dB(10,000,000,000,000 倍)比模拟输入端口。在 ADC 数字端口上的任何噪声。

设计中的信号完整性并不是什么神秘莫测的过程。 对于在设计的早期意识到可能潜在的问题是很关键的,同时可以有效避免由此在后期造成的问题。本篇讨论了一些关键的信号完整性挑战及处理他们的方法。

确保信号完整性:

1、隔离

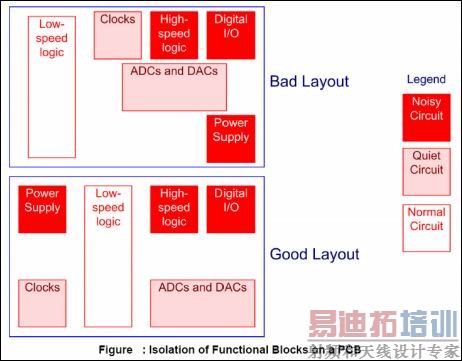

一块PCB板上的元器件有各种各样的边值(edge rates)和各种噪声差异。对改善SI最直接的方式就是依据器件的边值和灵敏度,通过PCB板上元器件的物理隔离来实现。下图是一个实例。在例子中,供电电源、数字I/O端口和高速逻辑这些对时钟和数据转换电路的高危险电路将被特别考虑。

第一个布局中放置时钟和数据转换器在相邻于噪声器件的附近。 噪声将会耦合到敏感电路及降低他们的性能。第二个布局做了有效的电路隔离将有利于系统设计的信号完整性。

2、阻抗、反射及终端匹配

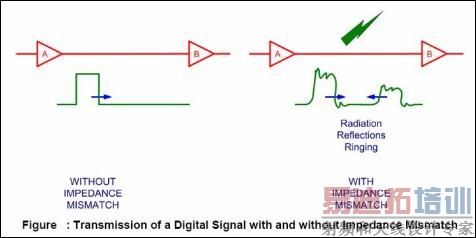

阻抗控制和终端匹配是高速电路设计中的基本问题。 通常每个电路设计中射频电路均被认为是最重要的部分, 然而一些比射频更高频率的数字电路设计反而忽视了阻抗和终端匹配。 由于阻抗失配产生的几种对数字电路致命的影响,参见下图:

a.数字信号将会在接收设备输入端和发射设备的输出端间造成反射。反射信号被弹回并且沿着线的两端传播直到最后被完全吸收。

b.反射信号造成信号在通过传输线的响铃效应,响铃将影响电压和信号时延和信号的完全恶化。

c.失配信号路径可能导致信号对环境的辐射。

由阻抗不匹配引起的问题可以通过终端电阻降到最小。 终端电阻通常是在靠近接收端的信号线上放置一到两个分立器件,简单的做法就是串接小的电阻。终端电阻限制了信号上升时间及吸收了部分反射的能量。 值得注意的是利用阻抗匹配并不能完全消除破坏性因素。然而认真的选用合适的器件,终端阻抗可以很有效的控制信号的完整性。

并不是所有的信号线都需要阻抗控制,在一些诸如紧凑型 PCI 规格要求中的特征阻抗和终端阻抗特性。

对于别的没有阻抗控制规范要求的其他标准以及设计者并没有特意关注的。 最终的标准可能发生变化从一个应用到另一个应用中。因此需要考虑信号线的长度(相关与延迟 Td)以及信号上升时间(Tr) 。通用的对阻抗控制规则是 Td(延迟)应大于 Tr的 1/6。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:PCB设计中铜箔的载流量分析

下一篇:PCB

Layout步骤简述