- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

DDR3 PCB Layout等长处理

录入:edatop.com 点击:

DDR3 PCB Layout等长处理

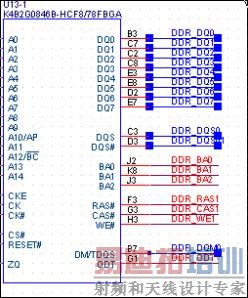

首先说下DDR3 数据线在原理图分布,以2 个DDR做示范。

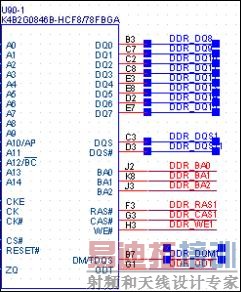

另一组在原理图分布:

我们分成2组,这里的差分线,是控制他们的数据线,如第一组是DDR0 到DDR7 加一个DDR_DQM0 线,DDR_DQS0 DDR_DQS01 就去控制这一组的数据线与CLK误差500MIL视规格书而定,有些规定数据线必须要达1000MIL,同组数据线误差10MIL 。不同组的数据线误差也是10MIL 。

下面再看PCB的高亮效果图,你会发现他们是很有规律蓝色是第一组,红色是第 2组。所以布局的时候,DDR数据线这头尽量靠近主芯片BGA。走线也近。

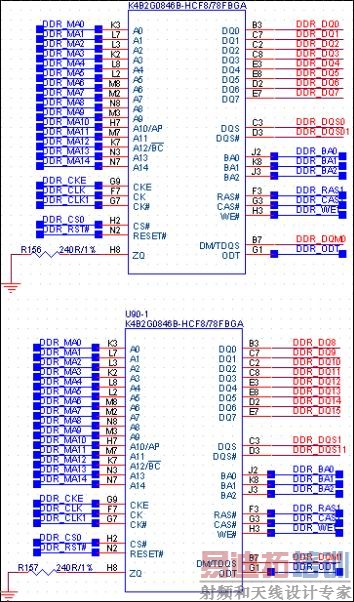

下面我们来说地址线和CLK原理图:

2 个DDR共用地址线和CLK。所以主芯片BGA到DDR1的距离,跟BGA到DDR2的距离要等长。也就是同一根地址线要等长正负10MIL 的误差,但地址线不可能跟数据线同组等长,所以与CLK 的数据是正负500MIL就可以误差看规格书 。

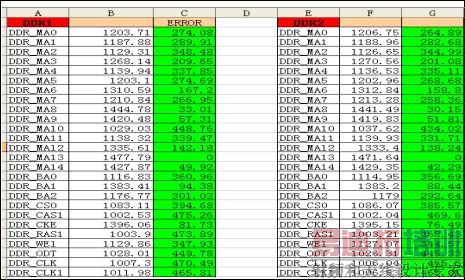

下面是做表格的情况,名字一样的误差都在10MIL 之内,但相对CLK他们误差在正负500MIL之内。

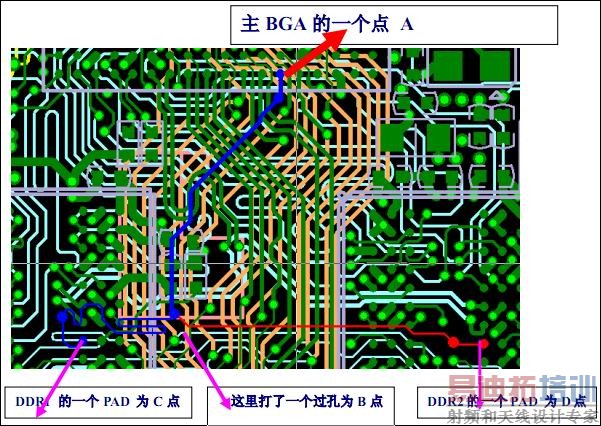

PCB效果

那么DDR1地址线的=A+B+C ,另一边的DDR2 地址线=A+B+D

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:高速PCB设计探讨(三)

下一篇:高速PCB设计探讨(二)

射频和天线工程师培训课程详情>>