- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速PCB设计仿真讲座四

1.2 高速PCB仿真的重要意义

1.2.1 板级SI仿真的重要意义

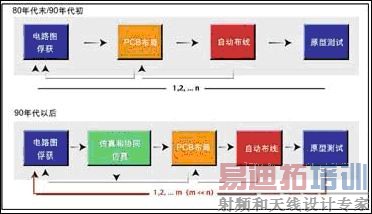

过去,PCB性能要采用一系列仪器测试电路板原型(通常接近成品)来评定。电路的复杂性增加之后,多层板和高密度电路板出现了,人们开始用自动布线工具来处理日益复杂的元器件之间的互联。此后,电路的工作速度不断提高,功能不断翻新,元器件之间连线的物理尺寸和电路板的电特性日益受到关注。

从根本上讲,市场是电路板级仿真的强劲动力。在激烈竞争的电子行业,快速地将产品投入市场至关重要,传统的PCB设计方法要先设计原理图,然后放置元器件和走线,最后采用一系列原型机反复验证/测试。修改设计意味着时间上的延迟,这种延迟在产品快速面市的压力下是不能接受的。

图 1 PCB 设计流程比较

“第一时间推出产品”的设计目标不只是一句广告词,事实上,这是生死攸关的竞争需要。在产品设计初期识别、预防和改正设计错误,可以防止电路板出错,这种操作模式比以往任何时候都至关重要,PCB 仿真就是最好的方法之一。板级仿真工具的作用就是在电路板制造前后帮助设计人员更快地开展调试工作。

Cadence 公司的PCB SI和SigXplor 设计工具为我们高速 PCB的仿真提供了强有力的手段,在系统方案设计与决策的时候,通过仿真往往能解决很多悬而未决的棘手问题,增加了对系统设计方案的可预见性,配合后端的 PCB设计与后仿真,能使我们从根本上解决高速信号的分析与处理问题。

1.2.2 系统级SI 仿真的重要意义

新一代的 EDA 信号完整性工具主要包括布线前/布线后 SI 分析工具和系统级 SI 工具等。使用布线前 SI 分析工具可以根据设计对信号完整性与时序的要求在布线前帮助设计者选择元器件、调整元器件布局、规划系统时钟网络和确定关键线网的端接策略。SI 分析与仿真工具不仅可以对一块 PCB 板的信号流进行分析,而且可以对同一系统内其它组成部分如背板、连接器、电缆及其接口进行分析,这就是系统级的 SI 分析工具。针对系统级评价的SI 分析工具可以对多板、连接器、电缆等系统组成元件进行分析,并可通过设计建议来帮助设计者消除潜在的 SI问题,它们一般都包括 IBIS 模型接口、2 维传输线与串扰仿真、电路仿真、SI 分析结果的图形显示等功能。这类工具可以在设计包含的多种领域如电气、EMC、热性能及机械性能等方面综合考虑这些因素对 SI 的影响及这些因素之间的相互影响,从而进行真正的系统级分析与验证。

对已经设计完成的系统的 PCB 进行后仿真发现信号完整性问题常常是非常被动的事,即使后仿真找到了问题所在,解决这些 SI 问题往往要从头再来,这样一来,既增加了设计成本,也发挥不了 EDA 设计工具对设计的指导作用,通过前仿真来决定系统的设计方案,可以有效的解决困扰我们的高速设计中的 SI 问题,将后续 PCB 设计的风险降到最低,这就是 PCB SI 和SigXplor 工具需要完成的任务。Cadence公司的 PCB SI 和SigXplor 设计工具可以仿真实际物理设计中的各种参数,对系统中的信号完整性和时序(timing)、串扰(Crosstalk)、EMI 问题进行定量的分析。

运用 PCB SI和 SigXplor设计工具进行系统级前仿真可以验证设计方案的可实现性,根据设计对 SI 与时序的要求来选择关键元器件、优化系统时钟网络及系统各部分的延迟、选择合理的拓扑结构,调整 PCB 的元器件布局、确定重要网络的端接方案。PCB SI和 SigXplor设计工具不仅可以对一块 PCB 板的信号流进行分析,而且可以通过设置 Design Link 对同一系统内其它组成部分如背板、接线器、Interconnect 线缆及其各个功能模块或插板进行综合分析,完成系统级的 SI 分析。针对系统级的 SI 分析工具可以对多板、接线器等系统组成部分进行分析,得出一系列的约束条件(Constraint)给系统的各个组成部分。在验证系统设计方案的同时得出解决 SI 问题的最大设计空间(Solution space),同样是我们 EDA 工程师的首要任务。

在系统级 SI仿真和设计验证中,点到多点的拓扑分析一直是困扰 SI 工程师的难点之一,随着总线频率的提高和器件的驱动能力、上升和下降延的特性差异,这些问题的解决起来越发困难,在系统背板设计过程中,还要考虑的系统对不同功能单元的兼容性,互换性、系统的满载和空载(如空载时残余导线对 SI 的影响)时,不同拓扑结构对 SI 的影响,要考虑到各个功能单元的最大时序余量,给它们更大的时序空间,增加模块的可实现性。目前,高速串行总线的应用在某种程度上缓解了高速系统设计中现的 SI 问题,LVPECL,LVDS 已经在很多高速系统中广泛采用,采用点到点的简单拓扑结构也可以避免不少高速设计问题。

系统级仿真的设计过程往往是一个不断反复的过程,通过仿真提高系统的兼容性,给各个功能模块或子单元最大的时序空间是我们追求的目标,同时,还要考虑到器件工作在最恶劣情况下(Worst case)系统的时序(timing),过冲(Overshoot,Undershoot),EMI 等方面的问题,这对于提高系统的稳定性和可靠性起到非常重要的作用。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...