- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速PCB设计仿真讲座三十一

第六章 后仿真过程及参数设置

后仿真,顾名思义就是工程项目后期阶段的仿真。针对电路板仿真来说,就是在电路板自动布线,及布线调整以后进行的仿真。

从仿真目的的角度来看,后仿真有两个目的:1、在自动布线及调整完成后,对于那些不能满足Electronic Csets 设计规则的网络进行拓扑调整,以放宽规则限制,这部分工作主要在 Topology Editor中完成;2、对于那些设计中的关键网络,在自动布线及调整完成后,要提取布线后的实体拓扑,进行重新仿真,以更精确的验证信号时序和波形是否满足设计要求。当然,就仿真的任务而言,后仿真和前仿真一样,基本上可分为四个:1、对时钟同步信号:仿真信号时序及信号质量,满足信号的建立时间、保持时间、小的过冲与振荡;2、对异步信号:仿真信号质量,满足信号的单调性、过冲容限及小的振荡;3、布线比较密的地方:仿真线之间串扰,确定不同间距的平行走线,能够容忍的平行长度。4、EMI 仿真。

后仿真较前仿真结果更精确,这是因为拓扑中的模型更精确。后仿真中拓扑中收发器模型由芯片生产厂家提供的 IBIS 模型转换而来,和前仿真时赋予各器件的模型是一样的,所不同的是传输线模型。前仿真拓扑中的传输线模型是理想模型即集中参数模型,就是仅仅用阻抗加时延来表示,而后仿真中的传输线则是用分散参数表示的模型(RLGC模型),由 Cadence 软件根据频率建立的 RLGC 矩阵,它充分考虑了电路板实际叠层要求的各信号层导线的不同参数,以及过孔等造成的阻抗不连续的影响,从而使得出的结果更接近实际。下面,我们将按照后仿真的两个不同的目的分别来介绍后仿真的过程及参数设置。

6.1 后仿真前的几个准备步骤

1) 首先检查已完成的 PCB上是否存有 DRC问题,有的 DRC问题会影响到后仿真结果。

2) 检查一下叠层参数是否设置正确,Cadence 软件自动计算的阻抗是否与期望值相近。

3) 将要仿真的信号走线调成与实际加工后的线宽一致 (表层有6.5mil调到5.5mil, 内层由6.5mil调到6mil)

6.2 针对目的一的后仿真

打开约束管理器看一下前面我们仿真的 D25_TCI 总线是否出现红色阴影,红色阴影表示该网络实际走线长度违反了设计规则,绿色阴影表示该网络实际走线长度符合设计规则。 (经检查 D25_TCI 走线长度符合设计规则,通常对于违反了设计规则的信号要重点仿真。)

获取错误信息后,就要设法改正,首先通过调节走线使其满足设计规则,对于那些和设计规则相差较大,和无法调节走线的网络就要根据实际情况调整拓扑,以放宽规则,然后重新仿真以保证你的改变符合要求。

这种情况的后仿真过程和前仿真相仿,详细的操作可参阅第四、五章的的相关内容。所不同的是仿真多了实际走线情况的约束,而且仿真的基本拓扑文件已经存在,所需做的只是修改走线长度及规则设置。

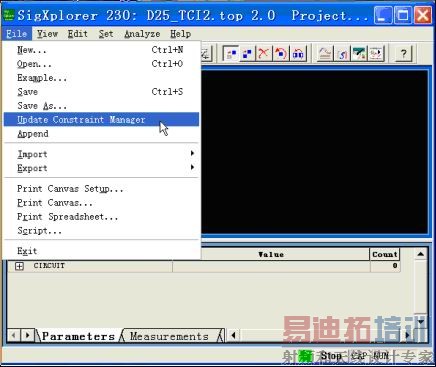

将规则放宽再进行仿真,如果仿真结果可以接受的话,则将放宽之后的新规则更新到 PCB文件中。在SigXplorer中更新了规则后, 在 File中选择 Update Constraint Manager (如图 8-1), 将自动更新 Constraint Manager中的约束条件,然后再将拓朴进行保存。

图 6-1 在 SigXplorer中更新 Constraint Manager

6.3 针对目的二的后仿真

目的二是对于那些设计中的关键网络,在自动布线及调整完成后,再提取布线后的实体拓扑,进行重新仿真,以更精确的验证信号时序和波形是否满足设计要求。仿真过程与以前的步骤是一致的,只是模型和参数有些改变。

6.3.1 进行仿真设置

1、 在 PCB SI 中打开所需后仿真的 brd 文件, 选择 Analyze=》 SI/EMI Sim=》 Preferences菜单, Analysis Prefences窗口打开,如图 6-2 所示

2、 在 Analysis Prefences框中选择 DevicesModels 标签。一般说来,PCB板上的器件都已赋予了经过验证的模型,所以该标签中的 Default IOCell Models项没有太大意义,我们所要做的是选择 Buffer Delay Selection中的 On-the-fly 项,如图 6-2 所示:

图 6-2 Analysis Prefences窗口

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:高速数字PCB设计方法

下一篇:高速PCB设计仿真讲座二十三