- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速PCB设计仿真讲座二十四

上面的两章主要是针对信号完整性来进行的仿真,时序的仿真过程与上述的是一致的,但时序还涉及到很多概念与数据计算,在这一章中主要讲述时序仿真的一些概念。

4.1 时序(TIMING)的一些参数

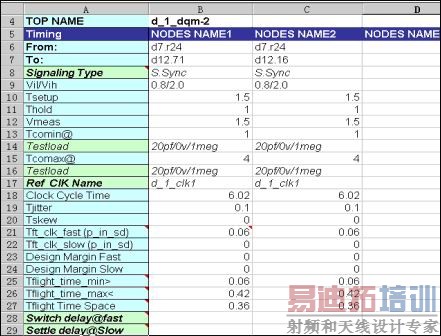

Cadence所完成的时序仿真实际上是建立在“Solution Space”的设计思想上的。所谓“Solution Space”就是通过分析电路原理、器件手册等资料得出一个理论的最恶劣条件下的时序最大可用空间,然后通过Cadence仿真软件计算出在满足该理论时序时对器件布局和布线的约束要求。在实践中我们总结了一张时序参数表格,如图 4-1所示(该表中的计算公式只是一种典型的时序分析,对于一些特殊的时序分析要根据具体情况定,但思想方法是一样的,有些参数在第四章已经作了说明) 。该表中行 4 – 24为理论参数,一般从器件手册中查找得到,行 25 – 27 为计算的理论结果,行 28、29为仿真结果。下面结合该表介绍时序仿真的过程。

图 4-1 时序参数表格

7、TOP NAME:是我们对要仿真的拓扑取的名字。该名字最好与相应的网络名相关。

8、From和 To:该两行分别填写驱动器和接收器的管脚号。采用:位号:管脚号格式。

9、Signaling Type:信号类型。对于信号类型我们定义为三种:源同步、外同步和异步。

在4.2 和 4.3 中会对这两种方式分别进行仿真过程介绍。

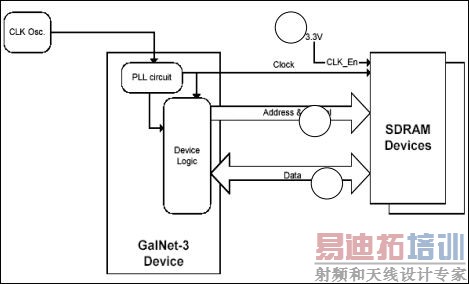

1)源同步:源同步也即是同步时钟由发送数据或接收数据的芯片提供。如图 6-2 所示。该图是 48520与 SDRAM的连接关系。①为源同步时钟,由 48520 提供;②为地址总线由 48520提供,单向;③为数据总线,双向。

2)外同步:外同步也即同步时钟的提供既不是数据发送芯片也不是数据接收芯片,而是由另外的时钟芯片提供。如图 4-2 所示。

3)异步:顾名思义是该信号没有时序要求。对于此类信号也就不存在时序仿真的问题。

图 4-2 源同步示例

图4-3 外同步示例

10、Vil/Vih:输入缓冲器的输入高电平和低电平值。

11、Tsetup:输入缓冲器要求的信号建立时间。

12、Thold:输入缓冲器要求的信号保持时间。

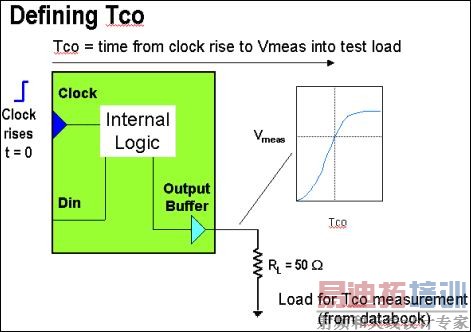

13、Vmeas:输出缓冲器的测量电压。

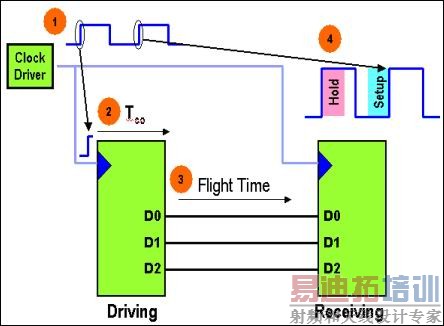

14、Tcomin/Tcomax:输出缓冲器的时钟到数据有效延时最小值/最大值。参考图 4-4。

图 4-4:Tcomin/Tcomax图示

15、Test load:Tcomin/Tcomax的测试条件。

16、Ref Clk Name:同步时钟的网络名。

17、Clock Cycle Time:同步时钟周期,单位 ns。

18、Tjitter:即同步时钟相位的抖动。

19、Tskew:同步时钟相位的偏移。

20、Tft_clk_fast/Tft_clk_slow:是同步时钟的 Flight time值。当时钟方向与数据方向同向时定义为正,反向时为负。对于该值的确定由时钟线的仿真结果确定。

21、Design Margin Fast/Design Margin Slow:设计余量。

22、Switch delay@fast/Settle delay@slow:该两项填写实际仿真结果,仿真结果应满足上面介绍的要求。一般说来应保证 Settle delay@slow满足要求,Switch delay@fast 在难以满足时可以适当放宽。

Tflight_time_min/Tflight_time_max:根据以上参数理论计算的空间范围

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:高速PCB设计仿真讲座三十二

下一篇:高速数字PCB设计方法