- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速PCB设计仿真讲座二十七

4.3 源同步接口仿真过程

源同步技术是指数据和时钟/锁存并行传输。由于源同步接口信号工作在“相对”的时钟系统下,这样对全局系统时钟的skew要求就可降低,在时序方程中就不需要flight time(飞行时间)这一变量,传输速率主要由数据和时钟/锁存信号间的skew决定,这样可以系统达到更高的传输速率。

源同步技术特点:

l 时钟/锁存信号与数据一起传送。

l 源同步技术中,接收端的建立和保持时间、skew决定了接口速度的极限,而走线长、Tco、器件本身的快慢不是影响接口速度的因素。影响速度的最主要因素是数据与时钟/锁存信号之间的skew,因此对数据和时钟/锁存信号间skew的约束是仿真中最主要做的工作。

l 迄今为止,每个源同步总线设计使用不同的方法,这就要求仿真环境必须能灵活适应每种要求,Cadence的Sigxp工具提供自定义测量(Custom Measurement)这一功能。需要注意的是测量数据信号相对与时钟/锁存信号的skew,而不是相对于主时钟;另外常常需要测量到die pad,把封装的影响因素考虑进去。

l 源同步接口一般速率高,这样码间干扰(ISI)就比较严重,所以经常会用到伪随机码序列来模拟各种码型的组合。在Sigxp中,可以通过设置Stimuli为Custom来实现,但是加到若干位后就不可以加了,如果想要加入较长的码序列,可以通过编辑拓扑文件(*.top文件)中Stimuli项PeriodicPatten下的序列来实现。一种简单的方法是,使用伪随机码产生程序生成任意长度的伪随机码序列,然后拷贝到*.top文件的相应位置。

另外在 Sigxp中还可以通过眼图分析仿真波形,通过对眼图高度和宽度的分析,可以得到反射、衰减、抖动等对信号的影响。在 Sigwave中可以将仿真出的伪随机码序列的串行波形叠加成眼图。在 Sigwave中GraphÆEye Diagram Performances中设置正确的信号周期,设置合适的 Offset值,以方便观察,然后选择GraphÆEye Diagram Mode,就可以得到相应信号的眼图。

4.3.1 源同步时序公式

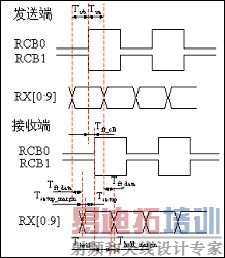

图 4-6 为源同步时序示意图,根据图 4-6 可得出相应的时序公式:

建立时间:

Tvb_min+Tft_clk_min-Tft_data_max-Tsetup-Tsetup_margin>0

保持时间:

Tva_min-Tft_clk_max+Tft_data_min-Thold-Thold_margin>0

其中:

Tvb:vb为valid before的缩写,表示驱动端数据在时钟有效前多少时间值有效;可以理解为驱动端的建立时间;

Tva:va为valid after的缩写,表示驱动端数据在时钟有效后保持有效的时间值;可以理解为发送端的保持时间;

Tft_clk:时钟信号的飞行时间;

Tft_data:数据信号的飞行时间;

Tsetup:接收端的建立时间;

Tsetup_margin:接收端建立时间的冗余量;

Thold:接收端的保持时间;

Thold_margin:接收端保持时间的冗余量;

4.3.2 源同步时序仿真过程

第一步:了解时序要求。

从数据手册中查到相应的时序参数,得到信号的时序要求。因为时钟和数据信号是由同一芯片产生,因而两者所处的环境(如电压、温度等)相同,可以认为两者的 flight time值的最大、最小值同时发生。

可得到如下结论:时钟、数据信号线的飞行时间必须严格相等(即 Tft_data_min=Tft_clk_max) 。因此在本例的仿真中,我们先对时钟、数据信号分别仿真,得到大致的拓扑约束,然后将时钟数据放在一个拓扑内进行仿真,测量接收端时钟数据的偏差,再用该偏差对时序进行微调验证。

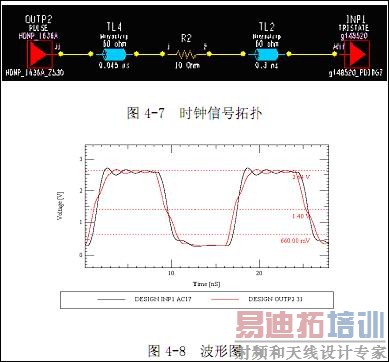

第二步: 时钟拓扑建立并仿真

这一步主要是对时钟的信号完整性进行仿真,得到接收端的时钟波形并检查测量。拓扑结构如图 4-7,波形如图 4-8。

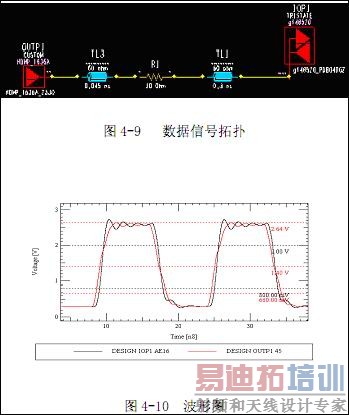

第三步:数据拓扑建立并仿真

这一步主要是对数据的信号完整性进行仿真,得到接收端的时钟波形并检查测量。拓扑结构如图 4-9,波形如图 4-10。

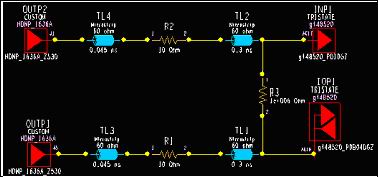

第四步:时钟、数据同时仿真

这一步中是将数据和时钟信号建立在同一个拓扑上,得到两者在接收端的波形,进行比对,验证时钟与数据信号在接收端是否满足时序要求。具体步骤如下。

a)建立拓扑结构

将时钟、数据拓扑建立在同一个拓扑上,实现方式是在数据和时钟信号间并一个无穷大电阻。拓扑结构如图 4-11。

图 4-11 时钟、数据仿真拓扑

b)设置相应的仿真参数

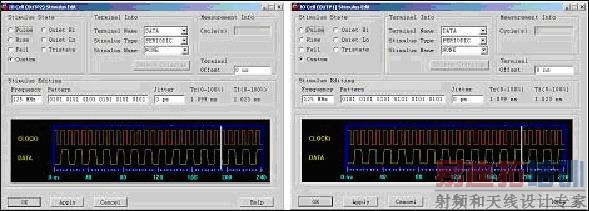

这一步骤中设置时钟周期、测量周期、偏移量、数据信号波形等参数,如图 4-12。

图 4-12仿真参数设置

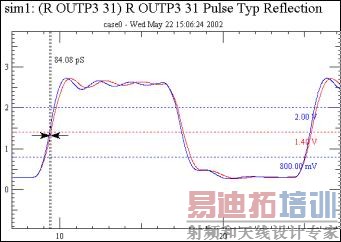

c)仿真得出波形并验证

仿真得到的波形如图 4-13。由图可知数据仅比时钟超前 84.08pS,可忽略,也可在拓扑中补偿,如果时钟与数据之间时间相差较大,就要通过调整拓朴结构进行改善。

图 4-13 时钟数据同时仿真波形

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:如何保证PCB铣加工的精度

下一篇:RF电路板设计的几个标准