- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速PCB设计仿真讲座二十五

4.2 传统的时钟同步系统仿真的过程

4.2.1 共同时钟同步系统的时序计算

传统的时钟同步技术是工作在“绝对”时钟的情况下,系统中采用同一个时钟,设计传统同步接口的主要工作是如何在系统中分配时钟,使得时钟线等长以减少skew。在CSSC系统中,信号传输时延或者说飞行时间增加了信号的建立时间,限制了系统的速度,尽管设计师们通过拓宽总线宽度来提高系统的吞吐量和带宽,但是这样成本和难度大大提高,对于更高速的系统,这种时钟同步技术已显得落后了。

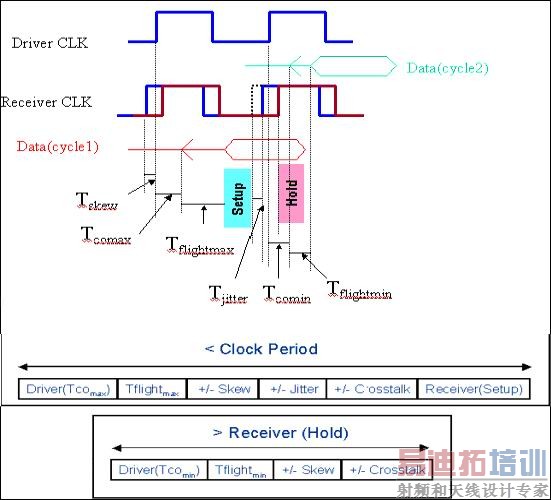

共同同步时钟的时序关系如下图所示:

图4-5 共同时钟同步系统的时序关系

根据以上时序关系和 4.1的时序参数得到下面理论计算的空间范围:

Tflight_time_min = Thold - Tcomin@ + Tskew + Tft_clk_min + Design Margin Fast+Tcrosstalk

该值与仿真结果中的Switch delay@fast相比较, 即仿真结果中的Switch delay@fast应大于Tflight_time_min。

Tflight_time_max = Clock Cycle Time - Tsetup - Tcomax -Tjitter - Tskew + Tft_clk_max - Design Margin Slow- Tcrosstalk

该值与仿真结果中的 Settle delay@slow相比较,即仿真结果中的 Settle delay@slow应小于Tflight_time_max。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:射频PCB设计注意事项二

下一篇:电路板设计电容摆放规则