- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速PCB设计仿真讲座二十六

4.2.2 共同时钟同步系统的仿真过程

时序仿真与信号完整性仿真过程是一致的,但前面要通过计算得到时序空间。下面简单介绍过程:

第一步:查阅有关芯片的 datasheet,以获取设计要求并将这些数据填写到电子表格中。电子表格中要求的数据,一般都能在芯片 datasheet 的 DC Characteristics和 AC Timing 两部分中查到。

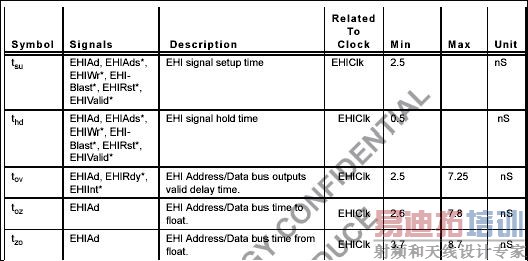

下表所示就是从 DATASHEET 分别查出的处理器与 MEMORY 的TCO/TSETUP/THOLD/TJITTER等参数:

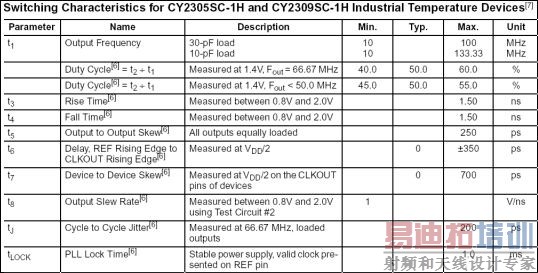

下面是时钟数据:

表 4-6 DATASHEET 参数

第二步:填写电子表格

在获取了这些资料之后我们就可以填写电子表格了,由于上面的数据线是双向的,所以我们按不同的方向分别填写表格,再按 23 提到的条件式计算出 Tflight_time_min 、flight_time_max 值。

第三步:建立拓扑进行仿真

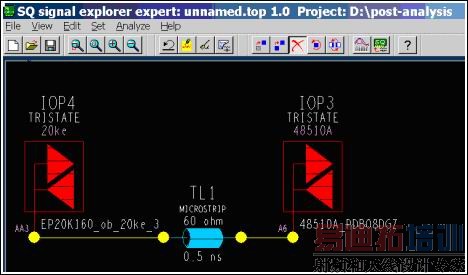

1、得到了我们设计要求的方案空间后,接下来就要开始建立拓扑了。可以从 PCB板上提取,也可以手工建立,然后进入到 SigXplorer中,仿真过程中以时间来定义 Tline。拓朴结构如下图所示:

图 4-7 拓朴结构

2、调节 Tline时间长度,在最大的时序空间内选取几个采样点,如下图所示:

图 4-8 参数范围

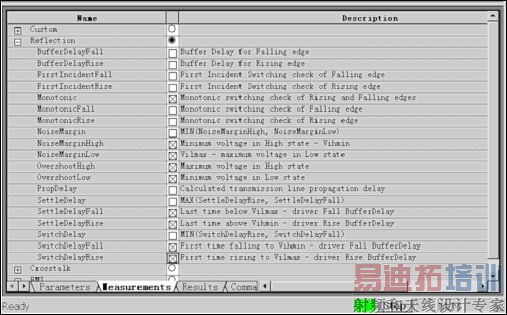

3、在 SigXplorer 窗口最底端选择 Measurements标签,点击 Reflection前面的“+”号打开测量反射参数的列表,在弹出菜单中选择需要测量的反射参数。

图 4-9 设置测量的反射参数

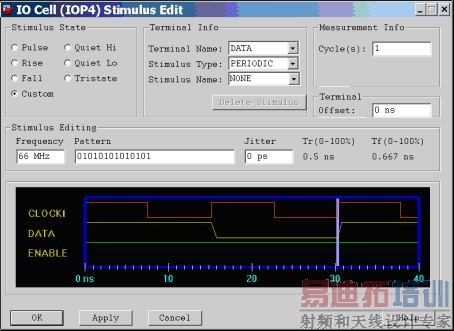

4、点 IOCell模型上的 TRISTATE,根据情况设置激励源的各参数如下图所示:

图 4-10 激励源设置

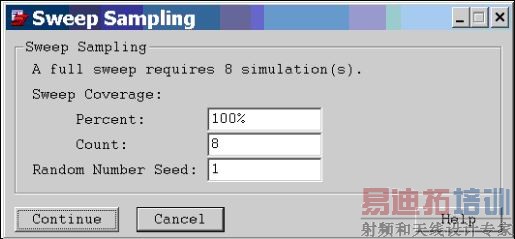

5、 点 Signal Simulate 图标进行仿真,出现如下界面:

图4-11 扫描仿真

点 Coutunue继续。

6、 查看仿真结果:

从 Rusult查看仿真结果是否满足要求,从仿真结果看,我们可以得知数据信号在两个方向上的时序是否都满足我们的设计要求(20ke->48510A:-1.25ns-6.95ns;48510A->20ke:-2.25ns-4.3ns) ,如果满足就说明我们的导线长度范围合理,能满足设计及布线要求;如果不满足,就要调整拓朴结构使之满足。

如果仿真的波形很差,如有很大的过冲和反射,这说明传输阻抗不匹配,如果发现了阻抗不匹配问题,接着就要想办法解决问题。解决的办法就是加源端匹配电阻。

第五步:改善拓朴并重新仿真

在 SigXplorer 中加入匹配电阻,调整拓扑,然后重新仿真,确定匹配电阻值和走线长度。 仿真过程在这里就不再详述,详细过程请参阅第三章中的相关部分。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:电路板设计中电容的去耦半径

下一篇:电源噪声是如何产生的?