- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速PCB设计仿真讲座二十九

第五章 设置约束及赋予PCB

按照前面的仿真过程,可以确定传输线的线长和拓扑形式,下面要把这些结果设置到相应的网络中,作为布线器的约束条件。对 Reflection有要求的信号通常添加长度约束、最大过孔数量约束和最大平行走线的约束(考虑串扰的时候),对于时序仿真的时候通常还要增加总线相对等长的约束(具体可参考《EDA工具手册》约束管理器分册)。

下面将讲述在 SigXplorer中怎样设置约束条件。

5.1 启动约束条件设置界面

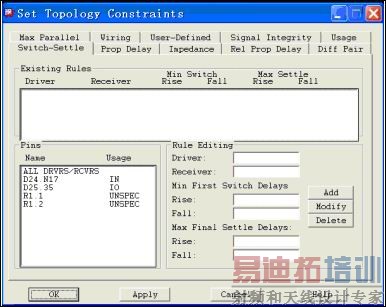

在 SigXplorer打开相应的拓朴结构,然后执行 Set -> Constraints…启动 Set Topology Constrains 界面,如图 5-1 所示:

图 5-1 Set Topology Constraints 界面

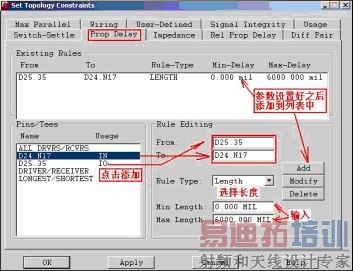

5.2 加约束的步骤

1、选择需设置的标签栏

2、 左边 Pins/Tees 列表里选择 From 的管脚

3、 左边 Pins/Tees 列表里选择 To 的管脚

4、在 Rule Type 的下拉列表中选择 Length

5、Min Length 输入约束的最短长度

6、Max Length 输入约束的最大长度

7、点击 Add 按钮添加

以上步骤在输入参数之后的会变成如下图所示的样子:

图 5-2 加约束条件的步骤

5.3 各个约束标签栏的作用

我们通常需要设置的有 Switch-Settle、Prop Delay、Rel Prop Delay和 Wiring等项,要根据仿真结果和实际情况来确定所需设置的项。设置步骤都如 7.2 所述,下面将详细地说明每个标签栏的作用。

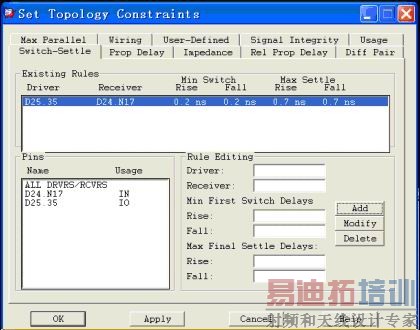

1) Switch-Settle 项,如图5-3 所示。

该项的内容为理论计算的值,为了以后核对方便,我们建议还是填写该项。填写时参考图6-1 中的电子表格。

23、 Driver:即表格中的 From内容,从左边的 Pins列表框中选取。

24、 Receiver:即表格中的 To内容,从左边的 Pins列表框中选取。

25、 Min First Switch Delays:Rise/Fall:该两项值填写一样,为表格中 Tfight_time_min值。

26、 Max Final Settle Delays:Rise/Fall:该两项值填写一样,为表格中 Tfight_time_max值。

27、 Add:为添加规则。

28、 Modify:为修改规则。

29、 Delete:为删除规则。

图5-3 设置 Switch-Settle值

2) Prop Delay 项,如图5-4 所示。

30、 From:约束传输线的起点节点名。

31、 To:约束传输线的终止节点名。

32、 Rule Type:规则类型,分为 Delay(延时) 、Length(长度)和%Manhattan(曼哈顿)长度百分比。可以选 Delay,约束延时时间;如果要约束线长,则选 Length。

33、 Min Delay:最小延时量。

34、 Max Delay:最大延时量。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:电容退耦的原理

下一篇:高速PCB画板功能分割