- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速PCB设计仿真讲座三十

3)Rel Prop Delay 项,如图 5-5 所示。

图5-5 设置 Rel Prop Delay值

对于一些有相对延时要求的网络,可以在该处设置相对延时值。

35、 Rule Name:相对延时网络的规则名,具有相同规则命名的网络为同一组相对延时网络。

36、 From:约束传输线的起点节点名。

37、 To:约束传输线的终点节点名。

38、 Scope:约束规则的适用范围。分为:Local 和 Global。Local为一个网络内部匹配,Global 为具有相同规则名的不同网络之间的匹配。

39、 Delta Type:Delta值的类型。

40、 Delta:相对约束值。

41、 Tol Type:误差类型。

42、 Tolerance:误差值。也就是允许相对约束值在多大范围内变动。

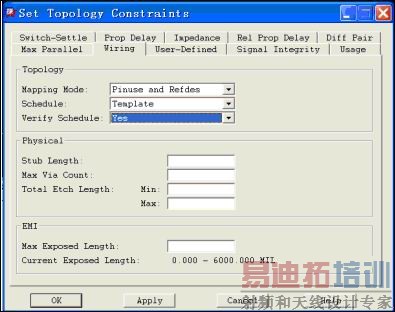

4) Wiring 项,如图 5-6 所示。

图 5-6 设置 Wiring 值

Topology组合框

43、 Mapping Mode:指拓扑结构与PCB中的网络结构之间的匹配方式。通常设为 Pinuse and Refdes。

44、 Schedule:拓扑结构类型,可根据具体的要求进行设定,如果没有特殊要求可使用 Template。

45、 Verify Schedule:选择 Yes。

Physical组合框

46、 Stub Length:Stub 长度。Stub 线俗称“线头”,比如菊花链形式的连线中进入管脚的分支线长度。一般可设一个小值。

47、 Max Via Count:网络中的最大过孔数。

48、 Total Etch Length:网络的总线长。

EMI组合框一般不设置。

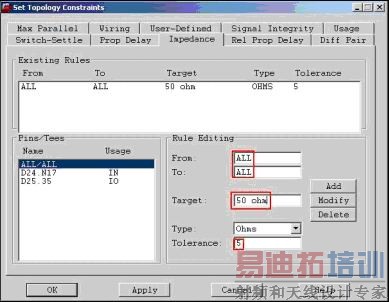

5) Impedance 项,如图5-7 所示。

可以对线路的阻抗进行约束,在 Impedence标签栏里面将阻抗 50Ω+/-5Ω加上:

图 5-7 设置 Impedance值

如果叠层参数没有设置正确,并且又在表层走线的话,这种阻抗约束起的作用不大。

5.4 将约束加到PCB文件上

这部份内容可参照《EDA工具手册》约束管理器分册,在其中已对这部份内容作了详细的说明,这里只举例讲述将约束条件加到 PCB的约束管理器的简单步骤:

1) 选择菜单 Constraints=》Electrical Constraint Spreadsheet或者点击工具栏图标,打开约束管理器,选择菜单 File=》Import=》Electrical Csets,在路径当中找到并选择加上约束的拓朴文件。

2) 选择左边的列表的 Electrical Constraint Sets=》All Constraints,点击拓朴名前面的“+”号,可以看到延迟的管脚对。

3) 选择左边的列表的 Net=》Routing=》Min/Max Propagation Delays

4) 用鼠标在网络列表里框选住适用此约束的网络, 或者按住键盘的 Ctrl 键然后再用鼠标逐一点取上述的网络,右键选择菜单 Create=》Bus,输入 bus 名,这时选中的网络已经被移到网络列表的上边了,并且是总线的形式。

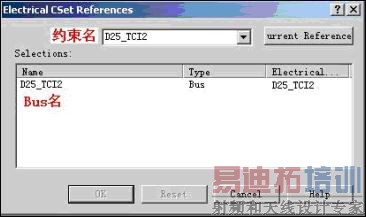

5) 点击该总线,再点击 Reference Electrical Csets列,出现的 Electrical Csets Reference 窗口,选择要加的约束名,如下图所示:

图 5-8 Electrical Csets Reference 窗口设置

6) 点击 OK 按钮关闭 Electrical Csets Reference 窗口

7) 点击 Colse 按钮关闭 Electrical Cset Apply Information 窗口

8) 点击总线前面的“+”号,可以看到 Propagation Delays 的约束已经加上了

9) 选择菜单 File=》Save,保存 PCB文件

这时,总线的约束已经被添加的 PCB文件当中,这时我们点击走线命令图标,然后在选择网络就可以看到该网络长度的动态显示,当这个动态显示呈现绿色的时候,标明是在约束范围内,如果呈现红色表明已经超出约束范围。

详细的约束管理器的内容请参见《EDA工具手册》的约束管理器分册。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:PCB设计中怎样合理选择电容组合

下一篇:电容退耦的原理