- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速PCB板设计技术一

如今,许多系统设计中最重要的因素就是速度问题。 66MHz 到200MHz 处理器是很普通的;233-266MHz的处理器也变得轻易就可得到。对于高速度的要求主要来自:

a) 要求系统在令用户感到舒适的、很短时间内就能完成复杂的任务。

b) 元件供应商有能力提供高度速的设备。

对 a 举例:即使产生最基本的计算机动画,也需要先计算大量的数据。目前,传播延迟4.5ns 的可编程 pld 设备已经出现,像 mach 这样的传播延迟 5ns 的复杂 plds 也已经存在。尽管它们看起来已经很快了,但是,使发展有潜力的并不是这些传播延迟绝对值,而是传播延迟可能达到的边缘极值(edge rate) 。将来会出现更快的设备,它们将具备更快的边缘极值。

设计高速系统并不仅仅需要高速元件,更需要天才和仔细的设计方案。设备模拟方面的重要性与数字方面是一样的。在高速系统中,噪声问题是一个最基本的考虑。高频会产生辐射进而产生干扰。边缘极值的速度可以产生振铃,反射以及串扰。如果不加抑制的话,这些噪声会严重损害系统的性能。

本文讲述了使用pcb-板设计高速系统的一般原则,包括:

l 电源分配系统及其对 boardinghouse产生的影响

l 传输线极其相关设计准则

l 串扰(crosstalk)极其消除

l 电磁干扰

1. 电源分配

设计高速系统板时需要考虑的重要问题就是电源分配网络。对一个无噪声系统来说,它必须有一个无噪声的电源分配网络。记住,如果想开发一个干净的 VCC, 那么得到一个干净的地就是十分必要的。对 AC 这个目的来说(这将是本文的讨论重点) ,VCC 就是基础地。

1.1 电源分配网络作为动力源

1.1.1 阻抗的作用

让我们考虑一块 5*5 的板子,数字 ICs,并有一个+5.0V 的电源。我们的目的是给位于板子上每一个设备管脚提供正好是+5V 的电压,不管这些设备管脚在板子上与电源的距离如何。再进一步,每个管脚上的电压应该是没有线噪声(Line noise)的。

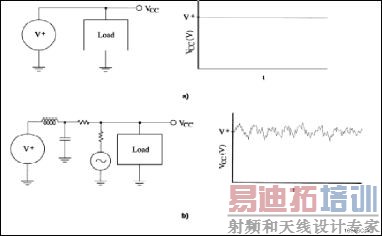

具有这些性质的电源表现为一个理想电压源(图 1a) ,它的阻抗为零。零阻抗可以保证负载与电压源恰好相等。 它还意味着噪音信号将被吸收, 因为噪音发生器有最小阻抗的极限。很不幸,这只是个理想条件。

图 1b 画出的是一个真正的电源,它有一定的以电阻,电感或者电容形式存在的阻抗。它们分布在整个电源分配系统中。因为有了阻抗,噪音信号也加入了电压(voltage)中。

图 1.1 电源模型

我们的设计目的是尽可能减小网络中的阻抗。有两种方法:电源总线法(power buses)和电源位面法(power planes)。一般来说,电源位面法较之电源总线法有着比较好的阻抗特征,不过,就实用性来说,总线法更好一些。

1.1.2 电源总线法 vs 电源位面法

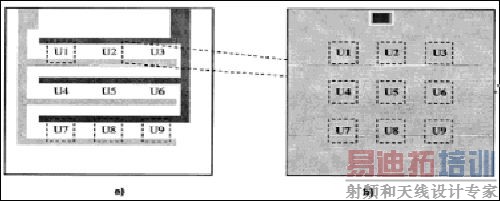

图 1.2 电源总线法和位面法模型

两种电源分配方案分别用上图 2 的a 和b 表示。

一个总线系统(图 2a)是由一组根据系统设备要求不同而具有不同电压级别的线路组成的。从逻辑上讲,典型的应该是+5V 和地线。每种电压级别所需的线路数目根据系统的不同而不同。

一个电源位面系统(图 2b)是由多个涂满金属的层(或者层的部分)组成的。每个不同电压级别需要一个单独的层。金属层上面唯一的缝隙,是为了布置管脚和信号过孔用的。

早期设计更倾向于总线方法,因为把整个层用作电源分配,成本比较高。电源总线与信号线分享那些层。总线需要给所有的设备提供电源,而且还要给信号线留出空间;于是,总线必须是很长很窄的带子。这使得在较小的交叉范围内产生一些小阻抗。

尽管这些阻抗很小,但是仍然很重要。一块最简单的PCB板也会有 20 到 30 个 IC。如果一个带有 20 个 IC 的板子上,每个设备有 200mA,那么总电流将为 4A。那么总线上 1.125欧姆的小阻抗将会造成 0.5V 的电压损失。如果供应的总电压是 5V 的话,那么总线上最后一个设备仅能得到 4.5V 的电压。

因为电源位面系统使用的是整个层,那么它的唯一限制就是板子的尺寸问题。带有同样多设备的系统,电源位面上的阻抗只是总线系统上的阻抗的一个零头。因此,电源位面系统似乎比总线系统更可能为整个系统提供全电压。

在总线上,电流被限制在总线的路线上。每个高速设备产生的线路噪声都将被带入这条线路中其他的设备。如图 2a 的板子,噪声由 U9产生,经总线带给 U7。

电源位面系统中,电流不受线路控制,分布在整个层上。由于整体阻抗小,电源位面系统比总线系统的噪声更小。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:印制电路板地线设计注意事项

下一篇:电源电子设备的电磁兼容性