- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速PCB板设计技术十

另外一项技术是将原来的终端电阻替换成为一个电阻和电容的串联-RC(series-RC)网络(图 25d) 。电阻值与 0 Z 相等。电容正常工作下可以是 100pF;精确的值并不重要。在这样的频率下,电容器是一个 AC 短路,但是它阻塞了 DC。于是驱动器(driver)看不到R L的 DC 负载效果(loading effect) 。这个技术被称为 AC 终端。

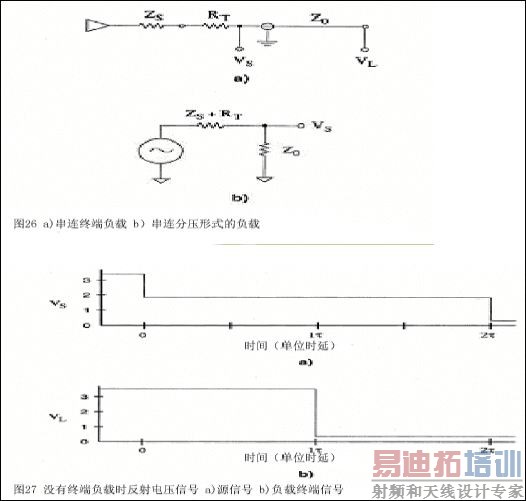

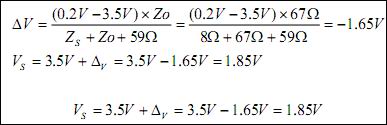

在负载端使用终端的技术,目的是减小第一次反射。另外一种方法是将一个电阻与源串联,增加Zs,使其等于 0 Z (图 25e) 。加上Zs后,这个电阻使得源阻抗看起来和 0 Z 一样。这样集中负载的终端效果最好,因为Zs 和Z0 分压使得信号削弱(图 26a,b) 。因为Zs+Rl=Z0,原来的传输信号被这个分压器分成了两半。半份信号沿传输线传输直到到达负载产生反射, 而负载是没有终端的。 由于反射的影响, 原来减为一半的信号增大了一倍,所以到达负载的信号又变回原值(图 27a) 。反射信号回到传输线,完成沿线路的传输过程(图 27b) 。

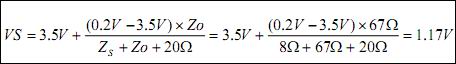

以上面我们讲过的没有终端的微波传输带放入一个串联的终端电阻为例。一个 59Ω的电阻(68Ω-9Ω)与电源串联。对一个从最低到最高的传输(transition) ,源信号是:

如果负载是一个开电路,那么产生-1.65V的反射。当反射回到源,由于Zs和Z0 在加入Rt 之后匹配了,Vs 是 1.85V-1.65V=0.2V。

当源信号到达的时候,负载的反射使得 VL 等于 0.2V。Vs 直到反射信号返回的时候才等于 0.2V,在例子中,是在 3ns 之后(图 27) 。

这种解决方案在负载分散在线路沿线的情况下有一定的风险,因为所有不在线的终端的设备都会收到一些中间电压的干扰,这些干扰直到反射返回源的时候才能清除。另外,这种技术会增大回路的延迟,因为在距离驱动器(driver)最近的设备确认输入有效之前,所有的信号不能被确认为有效。 而距离驱动器最近的设备只有在反射返回的时候才能确认输入有效。这样的时间延迟比前面提到的例子要长,因为分散的负载加入的电容减小了 0 Z ,增大了t PD。

尽管有这些缺点,串联终端的技术仍然在 DRAM 驱动器中得到了成功的应用,甚至在DRAM 是分散在信号线沿线的情况下也如此。 信号传输时间接近极限值, 如果精心挑选 Rt ,使得得到的Zs只比 Z0 略小,那么额外的延迟时间也会比减小。线上电压 swing 变大,电压水平接近 VOL,低于输入极限值。如果线是由 20Ω的电阻做的终端,那么Vs 变成:

因为终端不能够完全匹配,所以会产生一些振铃。但是,如果振铃达不到造成干扰的程度,终端方法仍然可以成功运用。设计者必须作出折衷选择。此外,高电容的 memory线经常 swamp out 振铃。

通常,由于高输出阻抗和低输出阻抗有区别,精确的终端匹配是不可能的。TTL兼容设备的输出阻抗在高电平与低电平的情况下是不同的。比如,PALCE16V8 在低的情况下为8Ω,而在高的时候为 50Ω。这样,选择合适的终端就变得复杂,因为没有一个单值同时适合这两种情况。必须选择一个折衷值,使得在两个传输方向都能得到可以接受的结果。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:高速PCB板设计技术六

下一篇:高速PCB板设计技术五