- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速PCB板设计技术十二

3. 色度亮度干扰

干扰(Crosstalk)是一种不希望产生的电路中的耦合信号。它可能是电容性的,也可能是电感性的,遵守下面的规则可以控制干扰。

3.1 电容性干扰

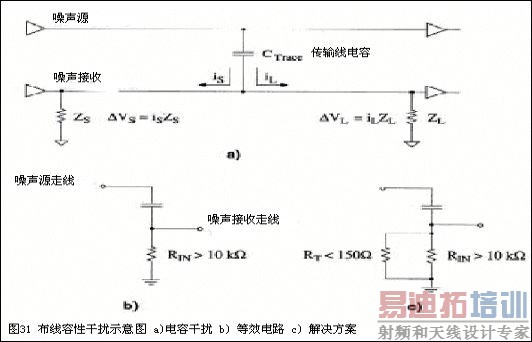

电容性干扰指的是信号线之间产生的电容性质的信号耦合。如果两条信号线靠得太近,就可能产生这样的干扰。

图 31 的电路表示了两条信号线,分别被称为噪声源和噪声接受者。由于线间有电容,噪声源的噪声会耦合到噪声接受者上。这一现象由噪声接受者被注入电流体现出来。在传输线中,电流在两个方向都碰到 0 Z ,并向两个方向传播,直到损耗在源或者负载为止。

因此而产生的电压毛刺(voltage spike)是由 0 Z 决定的。当电流脉冲到达Zs和 L Z 的时候都会在阻抗上损耗, 损耗的电压与阻抗成比例。 如果阻抗与源或者负载不匹配,反射就会产生。如果负载没有终端,通过 L Z 的电压毛刺可能非常严重。负载加终端可以有效减小下一个设备会接收到的电压噪声。

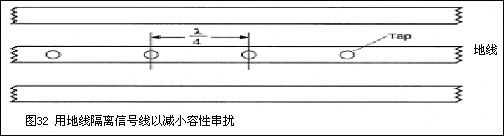

电容性干扰也可以用分离电路的方法减小。信号线距离越远,电容越小,干扰越小。由于板面空间会限制两条信号线之间的距离不可能太远。 另一个解决方案是在两条相邻的信号线之间加入一条地线。如图 32.这样信号与地线耦合,而不是与相邻的那条信号线耦合。

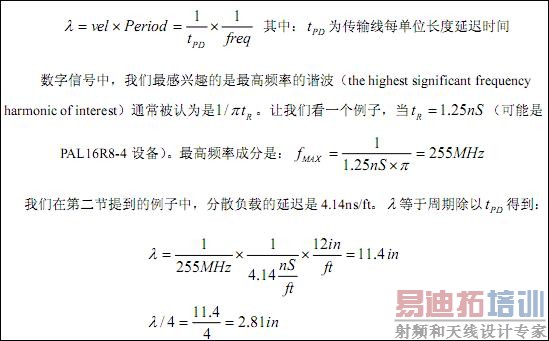

注意,地线必须接实地。如果它只接着电路终端(trace ends)的地线平面,电路会有相对较大的阻抗。一个良好的接地,地线应该用通孔(tap)连接地平面,tap 间距为最高频率信号成分波长的 1/4。

波长是信号一个周期传播的距离,或者是:

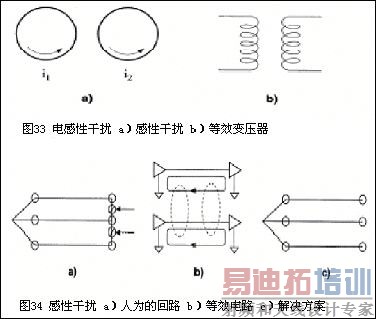

3.2 电感性干扰

电感性干扰可以被看作是一个多余的变压器(transformer)的初级线圈和次级线圈产生的耦合信号(图 33) 。变压器的线圈是PCB板子上(或者系统里的)电流回路。这线圈可能是由于不恰当的设计人为造成的(图34a), 也可能是信号线与信号回路组合自然造成的。(图34b) 。人为造成的线圈时常难以定位,但是可以被排除(图 34c)。

耦合给负载的多余的信号的大小依赖于线圈的大概尺寸,也依赖于被影响负载的阻抗。线圈尺寸越大,越紧密,传输的能量就越大。在次级线圈,负载端看到的信号随着负载阻抗的增大而增大。

3.2.1 线圈的尺寸和紧密程度

线圈的电感系数 L 随着线圈的大小增大而增大。当两个线圈互相作用,一个会产生初级电感(LP) ,另一个会产生次级电感(LS) ,如图 33b。由于信号线并不是有意设计成为变压器的,所以耦合很松散;但是仍然会对次级线圈产生干扰。

如果两条信号线的部分回路是一致的(coincide) ,产生的线圈可能造成自感变压器(auto-transformer)如图 35a, c。上面我们讨论过的 VME-背板就是这样一个例子。保证每条信号有自己的回路可以使这种干扰消除。

3.2.2 负载阻抗

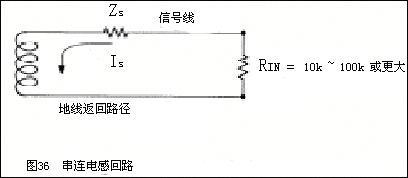

如果认为感性干扰是由形成线圈的环路产生的,解决的办法是将环路打开。很不幸,这样的环路很难定位。如果干扰是由于信号/信号回路线自然形成的,这样的环路是不能打开的。但是,减小负载阻抗可以将干扰减小。图 36 表示一个简化的带负载的次级“自然”环路设计方案。这里Zs是次级环路的固有阻抗。注意串联电流Is。因为阻抗是串联的,Is在环路中处处相等。Is一定,电压在最大的阻抗上降低得最多。在没有终端的线上,通常就是线上最终那个阻抗。如:在接收设备的输入端。

在输入端最不希望有大噪声,输入端期望最小的噪声。如果最大的信号经过最大的阻抗产生,通过在信号线接收端终端(terminating)可以减小输入端的产生的信号:将Rin减小到Rt。 Rt 通常在 30 到150 欧姆之间。Rin被减小了起码两个数量级。Rin上降低的电压也相应减小。降低的具体值很难预计,因为它还依赖于Zs,而Zs是很难预计的。但是Rin减小几个数量级会有明显效果的。

3.3 干扰解决方法总结

下面的步骤总结了减小干扰的方法。

1. 电容性和电感性干扰都随着负载阻抗的增大而增大。所以,所有可能产生干扰干扰的线都应该为线阻抗(line impedance)做终端(terminated)。

2. 将信号线分离,可以减小两条信号线产生的电容耦合能量的大小。

3. 电容性耦合可以通过用地线隔离的方法减小。为了起到良好效果,地线应该每隔λ/4英寸就与地平面连接。

4. 对电感性干扰,尽量减小环路大小。尽可能消除环路。

5. 对电感性干扰,避免出现共用信号回路的情况。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:高通MSM8X10芯片简介

下一篇:解决EMI传导干扰的几大方法