- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

DDR3 PCB设计-控制信号布线规则

录入:edatop.com 点击:

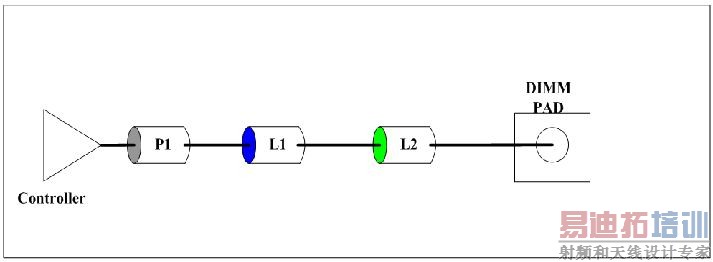

控制信号布线拓扑(DIMM)

| 参数 | 定义 |

| 信号组(Signal Group) | Control – CS#[3:0], CKE[3:0],ODT[3:0] |

| 拓扑(Topology) | 点到点信号,带有VTT 端接Point-to-Point with Parallel Termination |

| 走线层 | 内层(E or G) |

| 参考平面(Reference Plane) | 地平面 |

| 单端信号阻抗(Single-Ended Trace Impedance) | 40Ω+/-10% |

| 与非DDR3 信号的最小间距(Minimum Isolation Spacing to non-DDR3 Signals) | 25mil |

| 与其他DDR3 信号组的最小间距(Minimum Isolation Spacing to other-DDR3 Signal Groups) | 20mil |

| 封装长度的范围(P1, Package Length Range) | 730mil ~ 746mil (MC0)749mil ~ 767mil (MC1) |

| L1(Microstrip)(Fanout length segment) | 扇出线宽:4mil与其他DDR3 信号间距:4milL1 的长度应尽量短 |

| L2(Microstrip) | 与其他DDR3 信号间距:数据>20mil (trace-to-trace spacing > 4H)地址>20mil (trace-to-trace spacing > 4H) |

| 总的板级走线长度(Total Motherboard Length Limits, L1+L2) | Max = 3000mil |

| 信号的总长度限制-P1+L1+L2 | Max = 4000mil |

| 最大的过孔数(Maximum Recommended Via Count) | 2 个,信号换层时在信号线附近增加电源或地的过孔 |

| 控制信号与时钟对的长度匹配(包括封装长度) | CLK≤CMD≤CLK+500mil |

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:高密度PCB功能测试(1)

下一篇:电路板设计集成电路应用电路识

方法

射频和天线工程师培训课程详情>>