- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

L64724的卫星解码机顶盒设计(一)

1 概述数字压缩技术的发展,为卫星数字视频广播提供了有力的技术支持。目前虽然尚未形成全球公认的标准,但欧洲DVB-S的提出,无疑是一种可资参考的方案。L64724正是基于这一标准由LSI公司推出的一种性能较全面的数字视频卫星解码芯片。对系统设计者来讲,L64724能以最低的成本实现最大集成度和灵活性,而且在使用时外接元件最少。2 性能特点L64724具有以下特性:●可支持DVB和DSS系统;●BPSK/QPSK速率可达45兆波特;

●内含自动增益控制电源;●内含可编程维特比译码模块,包括1/2,2/3,3/4,5/6,6/7,7/8等各种速率,并能实现自动同步;●内含(204/188),(146/130)RS译码器;●可编程实现解交织、RS译码和解扰的同步;●对信道性能检测可自动监控;●卷积解交织的深度为12;●其串行主机接口与LSI逻辑串行控制总线接口兼容;●具有降压模式。

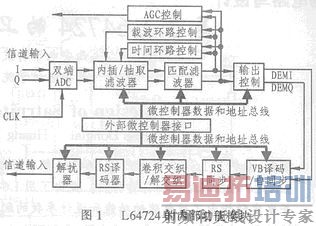

●内有滚降系数为20%和35%的平方根升余弦匹配滤波器;●具有可工作在1~45兆波特之间的反失真滤器,无须切换至外接SAM或低通滤波器;●可在片进行数字时钟同步和数字载波同步;●能通过芯片上的微控制器自动获取解调模式和调谐控制;●可用集成锁相环保证时钟同步;●具有快速信道切换模式;3 L64724的内部结构和引脚说明3.1 内部结构图1所示是L64724的内部功能图,它主要包含两个模块:BPSK/QPSK解调器和FEC译码器。图1中,数据和地址总线以上的部分为BPSK/QPSK解调器,以下为FEC译码器。

管 脚 | 说 明 | 备 注 |

CLK | RI/Q采样钟 | TTL输入 |

D[7:0] | 数据输入 | 双端TTL |

CS | 片选 | TTL上接输入 |

RESET | 芯片复位 | TTL输入 |

XOIN | 外部晶振输入 | CMOS输入 |

READ | 读定 | TTL上拉输入 |

CO[7:0] | 信道输出 | 三态输出 |

DBALIDOUT | 数据输出有效 | CMOS输出 |

ERROROUT | 错误指示 | 三态输出 |

LCLK | 输出时钟 | 输出 |

XOOUT | 输出到外部晶振 | CMOS输出 |

VDD | 数字电源 | 输入 |

VSS | 数字地 | 输入 |

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:联发科MTK平台发展及各芯片功能介绍

下一篇:通过飞线来调整PCB布线