- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

PCB电路板抗干扰技术设计

电磁兼容EMC是指电子系统在规定的电磁环境中按照设计要求能正常工作的能力。电子系统所受的电磁干扰不仅来自电场和磁场的辐射,也有线路公共阻抗、导线间辆合和电路结构的影响。在研制设计电路板时,我们也希望设计的印制电路板尽可能不易受外界干扰的影响,而且它本身也尽可能小地干扰影响别的电子系统。影响印制电路板抗干扰性能的因素很多,其中主要有铜箔的厚度,印制导线的宽度、长度和相邻导线之间的串扰,板内元器件布局的合理性,以及导线的公共阻抗、导线和元器件在空间产生的电磁场等。

设计印制电路板首要的任务是对电路进行分析,确定关键电路。这就是要识别哪些电路是干扰源,哪些电路是敏感电路,弄清干扰源可能通过什么路径干扰敏感电路。在模拟电路中,低电平模拟电路往往是敏感电路,功率放大器往往是干扰源。工作频率较低时,干扰源主要是通过线间桶合来干扰敏感电路;工作频率较高时,干扰源则主要是通过电磁辐射来干扰敏感电路。在数字电路中,高速重复信号.如时钟信号、总线信号等含有丰富的频率分量,是最大的干扰源,常对敏感电路构成威胁。复位电路、中断电路等是敏感电路,易受尖峰信号干扰,便数字电路不能正常工作。输人/输出电路(1/0)和外界相连,也应该特别注意。如果UO电路紧靠时钟线等干扰源,不需要的高频能量就会辆合到输人输出电线,电线上的噪声则会通过辐射或传导对电缆附近的敏感电路产生干扰。

在对电路进行充分分析,确定关键电路的基础上,还必须适当地在印制电路板上布置电路。如对于数字电路,应该把高速电路(如时钟电路、高速逻辑电路等)、中低速逻辑电路和UO电路布置在不同的区域,尽量在空间上把干扰源和敏感电路分开,这样可以使干扰源对敏感电路辐射干扰大大减小。

印制电路板抗干扰设计

PCB电路板抗干扰设计的目的是减小PCB电路板的电磁辐射和PCB电路板上电路之间的串扰。另外PCB的地线设计还直接影响1/0线缆的共模电压辐射。因此PCB电路板的抗干扰设计对于减小系统电磁信息辐射具有重要的意义。

PCB电路板的布局设计

印制电路板(PCB)的密度越来越高,PCB设计的好坏对抗干扰能力影响很大,所以PCB的布局在设计中处于很重要的地位。

特殊元器件的布局要求:

1.高频元器件之间的连线越短越好,尽量减少相互间的电磁干扰;易受干扰的元器件不能相距太近;输入和输出元件应尽量远离;

2.有些元器件有较高的电位差,应加大它们之间的距离,减小共模辐射。带高电压的元器件的布置要特别注意布局的合理性;

3.热敏元件应远离发热元件;

4.解辆电容应靠近芯片的电源引脚;

5.对于电位器、可调电感线圈、可变电容器、微动开关等可调元件的布局应按要求放在便于调节的位置;

6.应留出印制板定位孔及固定支架所占用的位置。

普通元器件的布局要求:

1.按电路的流程放置各个功能电路单元的器件,使信号流通方向尽可能一致;

2.以每个功能电路的核心元件为中心,围绕它来进行布局,元器件应均匀、整齐的排列在PCB上,尽量减少和缩短各元器件之间的引线和连接;

3.在高频下工作的电路,要考虑元器件之间的干扰,一般电路应尽可能使元器件平行排列,便于布线;

4.PCB的outplace一line离电路板边缘一般不小于80mil。电路板的最佳形状为矩形。长宽比为3:2或4:30。

PCB的布线设计

PCB的布线密度越来越大,因此PCB的布线设计尤为重要。

1.四层板电源线层应与地线层尽量靠近以获得最小电源阻抗。从上到下分别为:信号线、地线、电源线、信号线。考虑电磁兼容性,六层板从上到下最好为:信号线、地线、信号线、电源线、地线、信号线;

2.时钟线要与地线层相邻,线宽尽量加大,每根时钟线的线宽应一致;

3.与地线相邻的信号层布高速数字信号线和低电平模拟信号线,较远的层布低速信号线和高电平模拟信号线;

4.输入输出端布线应尽量避免相邻平行,避免发生反馈辆合;

5.印制导线拐弯处一般取135度钝角;

6.电源线、地线的线宽应尽量加大,对于0.5mm脚间距的器件布线宽度不小于12mil;

7.一般数字电路信号线宽度为8.il-10nul,间距6mi1-8mil;

8.解辐电容引线不能太长,尤其是高频旁路电容不能有引线;

9.混合信号电路板上的数字地和模拟地分割开,若布线跨越了分割间隙,电磁辐射和信号申扰都会急剧增加,产生电磁兼容问题。因此,PCB设计一般采用统一地,通过数字电路和模拟电路分区布局布线;

10.对于一些高速信号可采用差分对布线,减小电磁辐射。

试验事例

下面列出几个实际事例,说明不同原因带来的干扰及其实际解决办法。

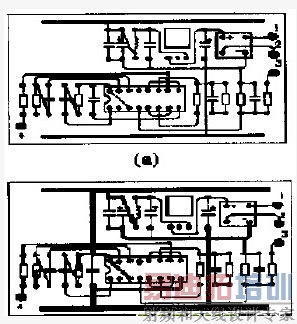

电源线和地线带来的干扰

上图取自某外协高压控保PCB的部分电路。(a)为原设计电路。由于电源线和地线的印制导线宽度太细,电路在工作时局受外界干扰;而(b)是经过改进后的电路,其电源线和地线加粗至5mm,解决了电路的干扰问题。

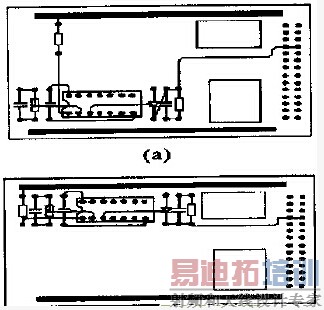

元器件布局不合理带来的干扰

上图取自某雷达发射机磁场控保PCB的部分电路。改进后的PCB电路(b)较改进前的PCB电路(a)在抗干扰性能上有很大的改善。

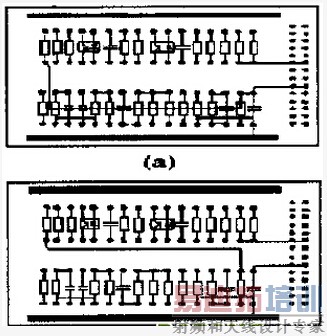

布线不合理带来的干扰

上图取自某雷达CFA电源控保PCB的部分电路。(a)为原设计电路。由于布线时将高压取样信号线布于闭环取样回路中,使闭环取样电路在工作时易受外界的干扰,造成经常误报过压故障;而(b)是经过改进后的PCB电路,由于避开了高压取样信号线带来的干扰,改进后的PCB电路工作可靠稳定。

结语

多层印制电路板具有独特的抗干扰特性,随着大规模集成电路、超大规模集成电路的不断发展,人们将越来越多地采用多层印制电路板。在现代电子系统中,随着时钟频率的提高,芯片集成度的增加,PCB设计的合理性和可靠性越来越重要,在设计中还需具体问题具体分析,以获得高质量的PCB设计。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:SAR

ADC

PCB板布局布线:参考路径

下一篇:多层线路板的诞生