- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

印制电路板特性阻抗的控制

一种好的叠层结构就能够作到对印制电路板特性阻抗的控制,其走线可形成易控制和可预测的传输线结构。

一、印制电路板特征阻抗

根据传输线理论和信号的传输理论,信号不仅仅是时间变量的函数,同时还是距离变量的函数,所以信号在连线上的每一点都有可能变化。因此定义连线的交流阻抗,即变化的电压和变化的电流之比为传输线的特性阻抗(Characteristic Impedance):

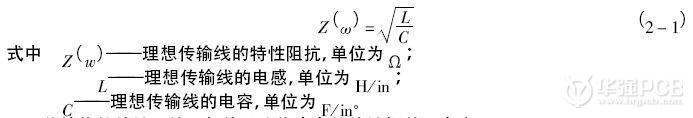

传输线的特性阻抗只与信号连线本身的特性相关。在实际电路中,导线本身电阻值小于系统的分布阻抗,特别是在高频电路中,特性阻抗主要取决于连线的单位分布电容和单位分布电感带来的分布阻抗。理想传输线的特性阻抗只取决于连线的单位分布电容和单位分布电感。

二、印制电路板特性阻抗的计算

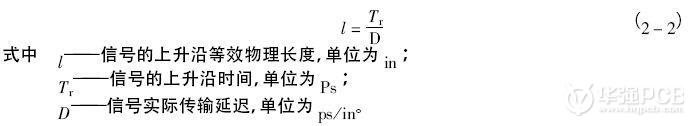

信号的上升沿时间和信号传输到接收端所需时间的比例关系,决定了信号连线是否被看作是传输线。具体的比例关系由下面的公式可以说明:

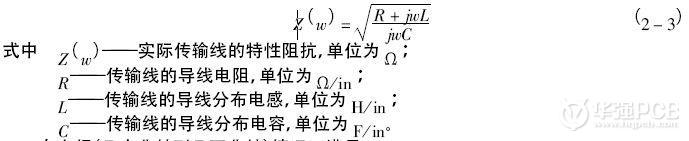

如果PCB板上导线连线长度大于l/b就可以将信号之间的连接导线看作是传输线。由信号等效阻抗计算公式可知,传输线的阻抗可以用下面的公式表示:

在高频(几十兆赫到几百兆赫)情况下满足wL>>R(当然在信号频率大于10 9Hz的范围内,则考虑到信号的集肤效应,需要仔细地研究这种关系)。那么式(2-3)可以简化为式(2-1)所示.

那么对于确定的传输线而言,其特性阻抗为一个常数。信号的反射现象就是因为信号的驱动端和传输线的特性阻抗以及接收端的阻抗不一致所造成的。对于CMOS电路而言,信号的驱动端的输出阻抗比较小,为几十欧。而接收端的输入阻抗就比较大。

三、印制电路板特性阻抗控制

印制电路板上导线的特性阻抗是电路设计的一个重要指标,特别是在高频电路的PCB设计中,必须考虑导线的特性阻抗和器件或信号所要求的特性阻抗是否一致,是否匹配。因此,在PCB设计的可靠性设计中有两个概念是必须注意的。

1 印制电路板阻抗控制

线路板中的导体中会有各种信号传递,当为提高其传输速率而必须提高其频率,线路本身若因蚀刻、叠层厚度、导线宽度等因素不同,将会造成阻抗值得变化,使其信号失真。故在高速线路板上的导体,其阻抗值应控制在某一范围之内,称为“阻抗控制”。

影响PCB走线的阻抗的因素主要有铜线的宽度、铜线的厚度、介质的介电常数、介质的厚度、焊盘的厚度、地线的路径、走线周边的走线等。所以在设计PCB时一定要对板上走线的阻抗进行控制,才能尽可能避免信号的反射以及其他电磁干扰和信号完整性问题,保证PCB板的实际使用的稳定性。

PCB板上微带线和带状线阻抗的计算方法可参照相应的经验公式。

(1)微带线。

PCB板上微带线阻抗的计算方法可参照下式:

H为两参考平面的距离,并且走线位于两参考平面的中间。此公式必须W/H<0.35及T/H<0.25的情况才能应用。

(2-4)和式(2-5)两个公式只是经验公式,如果要得到比较准确的结果,最好还是用仿真软件来计算。其他导线的阻抗可以根据PCB设计特性阻抗来计算。

2 印制电路板阻抗匹配

在线路板中,若有信号传送时,希望由电源的发出端起,在能量损失最小的情形下,能顺利的传送到接受端,而且接受端将其完全吸收而不作任何反射。要达到这种传输,线路中的阻抗必须和发出端内部的阻抗相等才行称为“阻抗匹配”。

在设计高速PCB电路时,阻抗匹配是设计的要素之一。而阻抗值与走线方式有绝对的关系。例如,是走在表面层(Microstrip)还是内层(Stripline/Double Stripline)、与参考的电源层或地层的距离、走线宽度、PCB材质等均会影响走线的特性阻抗值。也就是说,要在布线后才能确定阻抗值,同时不同PCB生产厂家生产出来的特性阻抗也有微小的差别。

一般仿真软件会因线路模型或所使用的数学算法的限制而无法考虑到一些阻抗不连续的布线情况,这时候在原理图上只能预留一些端接(Temninators),如串联电阻等,来缓和走线阻抗不连续的效应。真正根本解决问题的方法还是布线时尽量注意避免阻抗不连续的发生。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:高速串行总线的信号完整性验证

下一篇:如何解决EMI来提高多层PCB产品性能